FPGA最小系統(tǒng)電路分析:高速SDRAM存儲器接口電路設(shè)

高速SDRAM存儲器接口電路設(shè)計

本文引用地址:http://www.104case.com/article/189540.htmSDRAM可作為軟嵌入式系統(tǒng)的(NIOS II)的程序運(yùn)行空間,或者作為大量數(shù)據(jù)的緩沖區(qū)。SDRAM是通用的存儲設(shè)備,只要容量和數(shù)據(jù)位寬相同,不同公司生產(chǎn)的芯片都是兼容的。

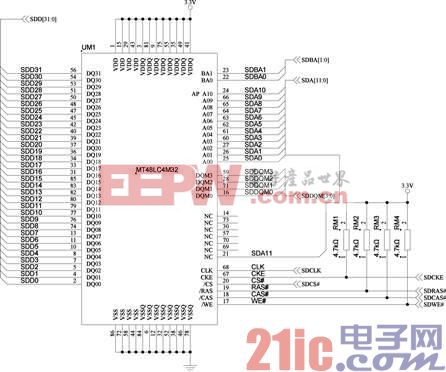

一般比較常用的SDRAM包括現(xiàn)代HY57V系列、三星K4S系列和美光MT48LC系列。例如,4M×32位的SDRAM,現(xiàn)代公司的芯片型號為HY57V283220,三星公司的為K4S283232,美光公司的為MT48LC4M32。這幾個型號的芯片可以相互替換。SDRAM典型電路如圖2.9所示。

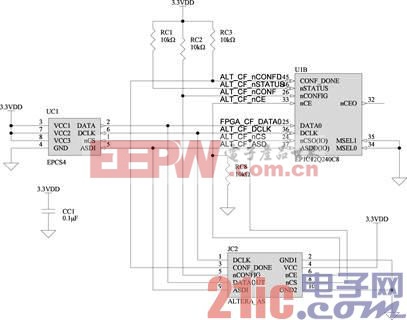

圖2.8 AS模式原理圖

圖2.9 SDRAM典型電路

評論