基于FPGA的手持式示波器設計

2 A/D轉換模塊

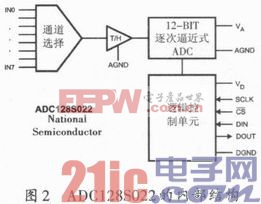

系統選用德州儀器公司(TI)的12位CMOS模/數轉換芯片(ADC128S022)實現模擬信號的數據采樣,該AD可以通過通道選擇信號實現8通道的模數轉換,并且是單電源供電;功耗極低,在2.7~5.25 V的供電范圍內,功耗只有1.2~7.5 mW;轉換速率可以達到50~200 KSPS,通過串行外設接口(SPI)與外部器件交換數據,芯片采用16引腳的超小型TSSOP封裝,這些特征都很適合小型的便攜式電子產品上使用,ADC12 8S022的內部結構如圖2所示。本文引用地址:http://www.104case.com/article/189496.htm

3 雙口RAM的讀寫控制

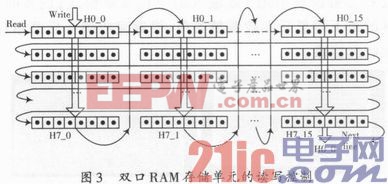

圖1所示手持式示波器設計結構中的雙口RAM的每位數據分別對應于LCD12864屏上的一個像素點,要求存儲容量8 192 b(1 024×8 b)。存儲器的管理需要滿足采集數據(64 b)按列實時寫入、又要滿足LCD模塊按行讀出數據(8 b)的要求。

為此,首先需要把64 b的圖形數據按位分成8段分別存儲在8個128x8 b的RAM單元中,這樣才能保證每個RAM存儲單元的讀/寫數據位寬一致。其次,采集的波形數據需要經過行列數據轉置模塊,才能做到RAM數據的按行寫入。行列數據轉置模塊采用了流水線結構,在觸發啟動信號和時鐘的共同作用下把采集到的列點陣數據轉置成適合LCD屏顯示的行數據格式。

圖3所示為雙口RAM存儲單元的讀寫順序示意;經過轉置后行數據,按照圖中所示的橫向“S”形順序寫入,而在數據讀出時,需要按照逐行的豎向的“S”形順序進行讀數據,這是LCD12864模塊控制時序要求的,按列逐字的寫入存儲器組織方式能夠提高RAM的緩存數據刷新頻率,同時也對存儲器的讀寫地址生成電路形成了較高設計難度。

fpga相關文章:fpga是什么

評論