全數字鎖相環的設計及分析

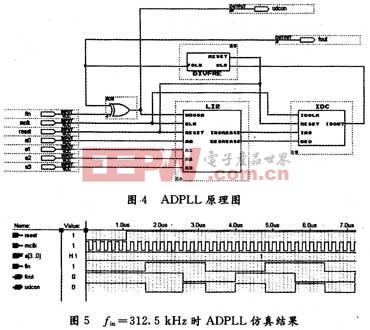

將環路各個模塊連接起來完成ADPLL的設計。為了簡化設計,將K變模可逆計數器的時鐘Mclk與脈沖加減電路時鐘2Nclk接在一起,fin等于環路中心頻率fc,fc=312.5 kHz。取M=16,N=8,Mclk=5 MHz。當a[3..0]=1時,設定K值為4。為了便于觀察,將K變模可逆計數器的輸入信號udcon引出。

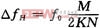

環路在進入鎖定狀態后,udcon為占空比為50%的方波。系統原理圖和仿真波形分別如圖4,圖5所示。

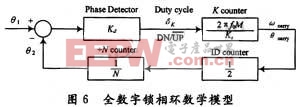

由 可得ADPLL的同步帶理論值為:f0/4,即234.375~390.625 kHz。根據仿真實驗結果,可以實現穩定鎖相的頻率范圍為:250~357.14 kHz,略小于理論值范圍。

可得ADPLL的同步帶理論值為:f0/4,即234.375~390.625 kHz。根據仿真實驗結果,可以實現穩定鎖相的頻率范圍為:250~357.14 kHz,略小于理論值范圍。

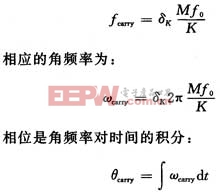

結合模擬和數字鎖相的理論分析,可以得到全數字鎖相環的相位和相差傳遞函數。圖6為全數字鎖相環的數學模型。

鑒相器可以看作增益為Kd的模塊,輸出占空比因子δk作為K變模計數器的輸入DN/UP,控制UP COUNTER和DOWN COUNTER的動作。

對于異或門鑒相器,相差等于π/2時,δk=1,相差等于-π/2時,δk=-1。因此對于異或門鑒相器增益Kd=2/π,同理可得邊沿控制鑒相器增益Kd=1/π。

K變模計數器產生CARRY信號的頻率為(f0為環路的中心頻率):

對于K變模計數器,其輸入輸出信號分別為δk和θcarry,對應的Laplace變換為δk(s)和θcarry(s),所以K變模計數器的相位傳遞函數為:

對于脈沖加減電路,由于每個CARRY脈沖使其輸出IDOUT增加1/2個周期,可以將他看作增益為1/2的模塊。除N計數器可以看作增益為1/N的模塊。系統的相位傳遞函數H(s)表示為:

為了獲得最小波紋,對于異或門(XOR)鑒相器和邊沿控制鑒相器(ECPD),K模值分別取為M/4和M/2,相應的時間常數分別為:τ(EXOR)= (N/8)T0,τ(ECPD)=(N/2)T0,其中T0=1/f0。由此可見,N越小,ADPLL的穩定時間越短。在本文中設計的鎖相環,Kd=2/π,M=16,N=8,K=M/4=4,代入時間常數公式可得:τ=T0。

5 結 語

本文介紹了一種一階ADPLL的設計方法,利用VHDL語言完成系統設計和仿真。ADPLL中可逆計數器的模值可以隨意改變,用來控制ADPLL的跟蹤補償和鎖定時間。除N計數器的分頻值也可隨意改變,使ADPLL可以跟蹤不同中心頻率的輸入信號。設計好的ADPLL模塊還可以作為可重用的IP核,應用于其他設計。同時,在理論分析的基礎上,建立了全數字鎖相環的一階數學模型,從而可以根據具體的設計要求定量的計算參數,簡化了ADPLL的設計。

低通濾波器相關文章:低通濾波器原理

塵埃粒子計數器相關文章:塵埃粒子計數器原理 鑒相器相關文章:鑒相器原理 數字濾波器相關文章:數字濾波器原理 鎖相環相關文章:鎖相環原理 鎖相放大器相關文章:鎖相放大器原理

評論