將汽車IC中的閂鎖敏感度降至最低

閂鎖測試

對于尋求通過汽車應用合格認證的器件而言,汽車電子理事會(AEC)Q-100文檔列出了IC閂鎖條件以及JEDEC標準IC閂鎖測試的參考資料。實際上,這兩個標準幾乎可以互換。

這些規范確定了兩類測試。其中,I類在室溫下進行,而II類定義為最大環境工作溫度。對于AEC Q-100合格認證而言,除非有特殊規定,II類通常在125℃條件下進行。

避免閂鎖的布線慣例

有多種布線技巧可用于消除或降低電路閂鎖的敏感性,包括從電源-電壓引腳配置等直接措施到各種更加復雜的措施。

標準的業界布線慣例包括:

每個阱必須擁有適當類型的襯底觸點

每個襯底觸點應該直接由金屬連接至電源墊片(supply pad)

將襯底觸點盡可能布置在接近連接至電源輸入軌的晶體管源極連接的地方(一條不太保守的準則是每5-10個

晶體管或每25-100μm間距布置一個襯底觸點)

配置n和p晶體管時,將n器件組合朝向VSS,而將p器件組合朝向VDD

連接P+保護環至n晶體管周圍的VSS

連接N+保護環至P晶體管周圍的VDD

保護環是布置在阱或電路簇之內或周圍的p+或n+擴散區域。這些保護環旨在提供連接襯底載流子的偏置擴散區域,從而對寄生雙極結構進行解耦。這些結構有兩種類型:少數載流子保護環和多數載流子保護環。

少數載流子保護環用于在少數載流子被反向偏置阱至襯底結匯集之前,匯集少數載流子,而在這個節它們可能會變為多數載流子。阱中的電流浪涌可能會導致壓降大至導通寄生雙極,從而引發閂鎖。

多數載流子保護環把多數載流子電流引發的壓降減至最小來對寄生雙極晶體管進行解耦。同樣,阱中的電流浪涌會導致壓降大至能夠導通寄生雙極,從而引發閂鎖。

對接觸點(butted contact)與閂鎖相關,因為它們有效降低基極-射極分流電阻(R2)。理想的布線將取決于這些射極(N阱中的擴散區)是否以真正對接觸點或反相偏置阱結的形式連接起來,或保留在漂浮狀態以及它們的相對尺寸。這樣一來,恰當地對其布線相對簡單,但要確定的話則有點復雜。

然而,考慮到噪聲問題,混合信號IC的設計規則不允許對接觸點。相反,多種保護條和/或單獨電源域可以考慮用于數字和混合信號應用。

寄生雙極基極寬度也已經被分析,以確定它對閂鎖敏感度的影響。p+射極和阱形成掩模邊緣(Xp)之間的間隔影響相對小,n+射極和n阱邊緣(Xn)之間的間隔影響更大。

NPN射極閂鎖觸發電流有兩種競爭的影響:R2隨著Xn增加和βnpn降低以增加Xn。然而,R2的增加相對于Xn值較小時占據大部分,而在Xn值較大時電流增益(βnpn)中的變化成為主要影響。因此,與自然假設相反,較寬的結構實際上可能對閂鎖更敏感。

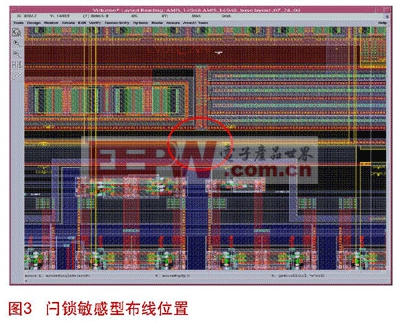

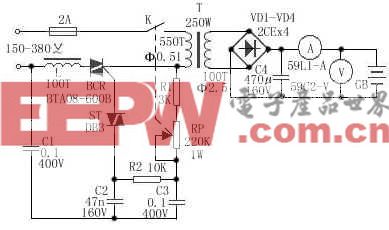

圖3顯示閂鎖問題布線的一個例子。紅圈區域是用于數千微米寬的20V PMOS器件(圈中黑色部分)的電阻n阱結。問題在于阱結的退出通道使用從阱到電源串聯在一起的較小晶體管。這就設置了一個與N阱結串聯的適當阻抗,而N 阱結將以極低的電流電平正向偏置寄生PNP晶體管的基極-射極結。

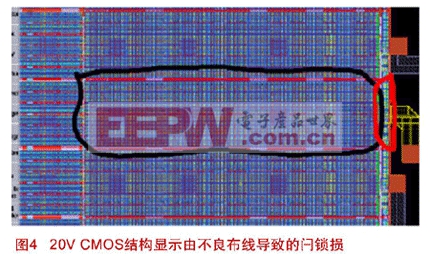

圖4顯示另一個有問題布線的例子,其中較小簇的數字邏輯布設在近鄰高壓I/O單元處。圖中顯示物理上最接近墊片(pad)的標準單元門已經被驅動至閂鎖并且被損壞。在隨后的修改中,邏輯被移至更遠,但僅在應用了保護條時器件才會通過閂鎖。物理隔離并不會確保閂鎖免疫。互補保護環有必要恰當地匯集由I/O注入的少數載流子和多數載流子。

其它考慮

外延起動材料的使用已經成為降低閂鎖敏感度的一個非常流行的選擇。本質上講,輕微摻雜質的外延層為IC提供高質量硅片,而較多摻雜質的襯底則從工作的器件區域吸收雜散電流。輕微摻雜質的外延層和較多摻雜質的襯底形成的結提供內置場,將多數載流子引導至襯底,注入的少數載流子也反射回外延層。結合的影響就是使保護環更加有效。

最后,ESD保護結構會影響閂鎖性能。簡單的二極管結能夠分流可能造成潛在有害的電流。這會增加給定輸出拓撲結構的閂鎖免疫性。相反,具備雙極特性的 ESD保護結構(如驟回或SCR結構)可能擁有低至足以被閂鎖應力觸發的維持電流。因此,必須注意確保ESD結構在合理的過應力狀況期間不工作。

結論

汽車工業中存在的嚴格元件認證程序要求芯片設計人員從項目的最早階段就可恰當地解決閂鎖故障方面的潛在問題。未能滿足特定的免疫性要求,可能導致延遲或重新開始的設計工作,這將會使成本更為高昂。

第一步的分析能夠預測閂鎖閾值,而這應針對創建片外連接的任何晶體管而進行。配備這方面的基礎信息,設計人員就能夠運用最佳的布線慣例來減輕閂鎖敏感性。單獨對晶體管進行物理隔離并不足以滿足AEC-Q-100或JEDEC閂鎖標準,雖然起始材料的選擇將影響器件對閂鎖的敏感度。建議設計人員在考慮閂鎖的同時也采取措施確保ESD免疫性,增強ESD保護措施,而非削弱閂鎖免疫性。

評論