∑-△ADC的降采樣濾波器的設(shè)計(jì)與實(shí)現(xiàn)

本設(shè)計(jì)中,k=4,c=1 617.19,f=166 kHz時(shí)Magnitude=0.999 947,滿足ENOB為14 bit的要求,并為后面的設(shè)計(jì)留下16 kHz的冗余空間。

3.3 FIR半帶濾波器

FIR型半帶濾波器是一種特別適合實(shí)現(xiàn)D=2倍降采樣的線性相位濾波器,其硬件結(jié)構(gòu)非常簡單,因此在降采樣系統(tǒng)中的最后一級一般都采用半帶濾波器。

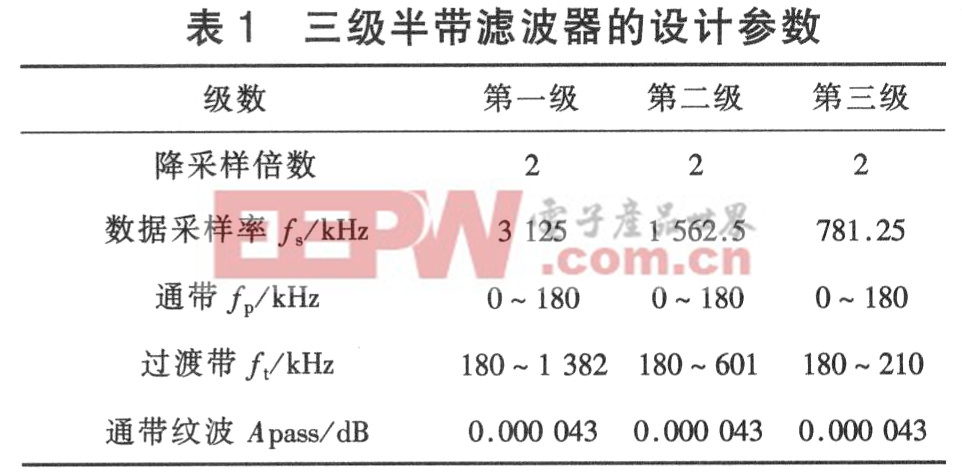

根據(jù)∑一△ADC的技術(shù)指標(biāo),可以得到三級半帶濾波器的設(shè)計(jì)參數(shù),如表1所示。本文引用地址:http://www.104case.com/article/188975.htm

通帶設(shè)為O~180 kHz,是為了保證0~150 kHz帶寬內(nèi)均能滿足指標(biāo)要求。通帶紋波取0.000 005(0.000 043 dB),是為了滿足設(shè)計(jì)的有效位數(shù)為14 bit,并且考慮到尾數(shù)舍入等非理想因素的存在。

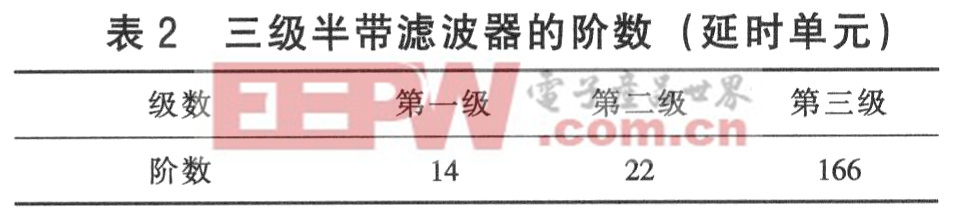

根據(jù)表1,調(diào)用Matlab 7.O中的工具箱組件filter design,得到三級半帶濾波器的系數(shù)。表2分別列出了三級半帶濾波器的階數(shù)(延時(shí)單元)。

3.4 系統(tǒng)仿真與驗(yàn)證

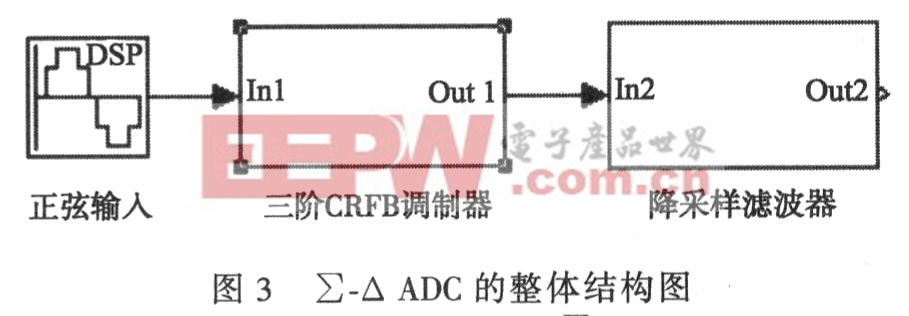

實(shí)現(xiàn)∑-△ADC的整體結(jié)構(gòu)如圖3所示,抽取濾波器由Sharpened CIC濾波器、ISOP濾波器和三級半帶濾波器組成。Sharpened CIC實(shí)現(xiàn)16倍抽取,三級半帶濾波器實(shí)現(xiàn)8倍抽取。

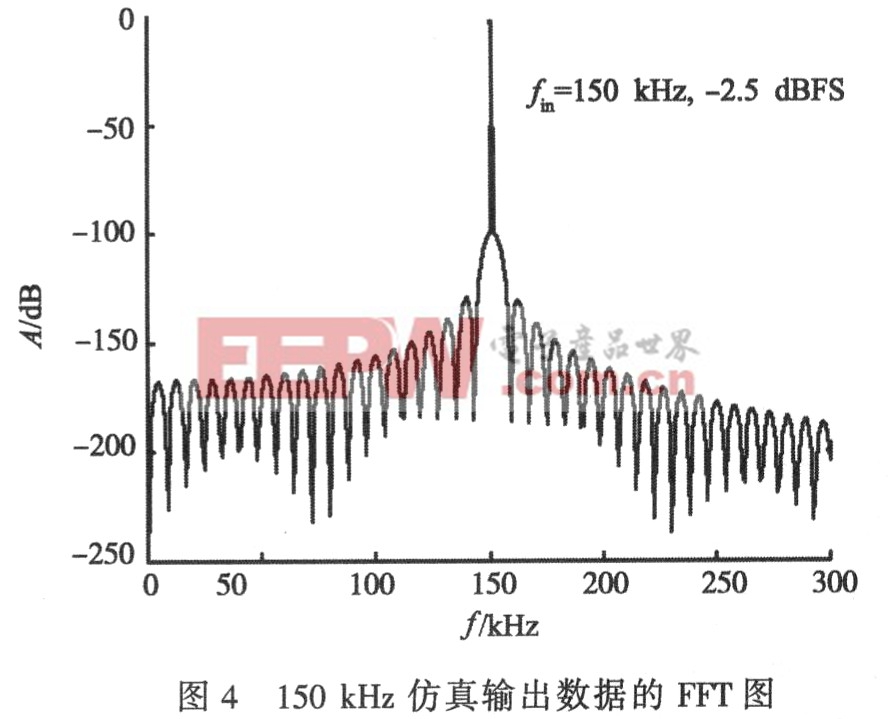

圖4為150 kHz輸入信號(一2.5 dBFS)仿真輸出數(shù)據(jù)的FFT圖。表3、4、5分別為SINAD、SFDR和THD的仿真數(shù)據(jù)。

4 降采樣濾波器的ASIC設(shè)計(jì)

4.1 電路設(shè)計(jì)

本設(shè)計(jì)用Verilog硬件描述語言描述電路,采用Synopsys的Design Compiler進(jìn)行綜合。

4.1.1 濾波器系數(shù)優(yōu)化

本設(shè)計(jì)采用CSD碼(canonical signed-digit)來表示量化后的系數(shù)。和二進(jìn)制代碼相比CSD碼采用0、l和一1來表示一個(gè)數(shù),具有非零位的個(gè)數(shù)最少、每一個(gè)非零位的相鄰位必為零的特點(diǎn)。

4.1.2 乘法器設(shè)計(jì)

本設(shè)計(jì)中乘法器單元的上限定為16×16,本文采用了Synopsys提供的DesignWare庫中的16×16乘法器單元,該單元的設(shè)計(jì)和綜合都比較成熟,通過Design Compiler綜合后面積和速度的優(yōu)化都比較理想。對于位數(shù)高于16 x 16的乘法器,本文以16×16乘法器單元先進(jìn)行低位乘法運(yùn)算,再進(jìn)行高位乘法運(yùn)算,最后再將高低位結(jié)果移位相加得到最終的乘法結(jié)果。

4.1.3 各級間輸入輸出位數(shù)的確定

評論