轉(zhuǎn)換器時鐘技術(shù)向高速數(shù)據(jù)時鐘發(fā)展

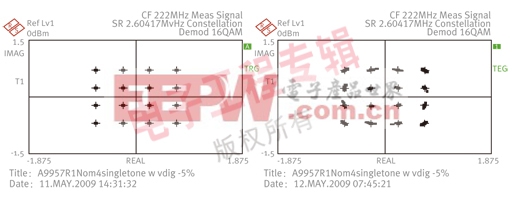

采樣時鐘相位噪聲對DAC的影響通常表現(xiàn)為調(diào)制信號的誤差向量幅度(EVM)有所降低。對于給定的調(diào)制方案,高相位噪聲有效地影響星座點(diǎn)使EVM下降并潛在地提高了誤碼率。圖7所示的16 QAM星座圖中體現(xiàn)了這一點(diǎn)。圖7(a)展示了干凈時鐘條件下的星座圖。圖7(b)展示了高相位噪聲時鐘對星座圖的影響。相位噪聲事實(shí)上旋轉(zhuǎn)了降低相鄰點(diǎn)噪聲容限的星座點(diǎn)有效相位。應(yīng)當(dāng)注意的是,寬帶相位噪聲和抖動也會降低EVM。在帶通濾波用于DAC輸出的應(yīng)用中,主要的考慮事項(xiàng)就是近載波相位噪聲。本文引用地址:http://www.104case.com/article/188853.htm

圖7:(a)干凈時鐘的16QAM星座圖。(b) 帶高相位噪聲的時鐘對星座圖的影響。

顯然,時鐘的頻譜純度是收發(fā)器時鐘解決方案的一個關(guān)鍵方面,但人們還期望時鐘系統(tǒng)能提供其他一些功能。

回到圖1可看到,該收發(fā)器具有多個接收通道,每個都需要單獨(dú)的ADC。在某些情況下,也會使用多個DAC通道。可能需要額外的時鐘通道來為用于數(shù)字預(yù)失真、FPGA或基帶ASIC芯片的ADC提供時鐘。

DAC和ADC編碼率通常各不相同。FPGA和基帶元器件也可能需要不同的頻率。頻譜干凈的主時鐘信號需要單獨(dú)分配給每個通道,為該通道分頻為所需的頻率,然后轉(zhuǎn)換成適當(dāng)?shù)妮敵鲂盘柛袷健我皇瞻l(fā)卡的輸出信號通常混合了LVPECL、LVDS和CMOS格式。兩個通道之間往往要求偏斜很緊密,以限制PCB布線的延遲變化。在某些情況下,在兩個時鐘之間設(shè)置延遲或相位偏移是必要的。在轉(zhuǎn)換器采樣時鐘和用于將ADC輸出數(shù)據(jù)鎖存到基帶芯片的時鐘之間可能需要這樣做。

在這些系統(tǒng)中,通道與通道之間的耦合是一個需要考慮的因素。如前所述,DAC和ADC時鐘通常運(yùn)行于不同的頻率。通道之間的耦合,或時鐘從一個通道向另一個饋送可能會在采樣時鐘上導(dǎo)致不想要的雜散音。有用的時鐘信號和無用的噪聲可能會導(dǎo)致產(chǎn)生乘積混頻,這可能在有問題的地方產(chǎn)生毛刺。如果混頻發(fā)生在編碼輸入處,這些問題有時可通過在主時鐘和輸入時鐘邊沿及時進(jìn)行偏置而得到緩解。具備調(diào)節(jié)每個低抖動時鐘延遲的能力可以成為時鐘系統(tǒng)的一項(xiàng)優(yōu)勢。

為了盡量減少系統(tǒng)宕機(jī)時間,在輸入?yún)⒖汲霈F(xiàn)故障的情況下,時鐘系統(tǒng)應(yīng)提供“備份”功能。這可通過增加第二個參考輸入來實(shí)現(xiàn),在主參考出錯的情況可以切換到這個備份參考輸入。這種備份時鐘的指配有時被稱為“時鐘冗余”。監(jiān)測主時鐘、檢測故障然后切換到備份的能力被稱為“參考切換”功能。

對于主時鐘和輔時鐘均出現(xiàn)故障的情況,可實(shí)施另一層保護(hù)功能,被稱為“保持(holdover)”。在保持模式中,時鐘系統(tǒng)進(jìn)入一種模式,即在輸入失效之前盡可能長時間地保持時鐘頻率。對于給定的時鐘系統(tǒng),保持的準(zhǔn)確性和持續(xù)時間取決于時鐘電路架構(gòu)。本文第二部分在討論網(wǎng)絡(luò)時鐘時對此會有更詳細(xì)的闡述,因?yàn)槟切┫到y(tǒng)中的保持模式要嚴(yán)格得多。對于收發(fā)器系統(tǒng),保持模式并不試圖讓收發(fā)器工作在它的正常性能水平,而是要保持足夠的時鐘功能,如可生成適當(dāng)?shù)南到y(tǒng)警報(bào)以啟動系統(tǒng)修復(fù)。

總而言之,多種多樣的系統(tǒng)需求廣泛存在,以支持各種各樣的空間標(biāo)準(zhǔn)、系統(tǒng)通道數(shù)要求和架構(gòu)方案。這些系統(tǒng)的時鐘必須足夠靈活,以適應(yīng)廣泛的應(yīng)用、保證系統(tǒng)可靠性并且還能夠提供轉(zhuǎn)換器所要求的極低抖動和相位噪聲。

(1) AD9445:14位125MSPS , IF采樣ADC

(2) ![]()

(3) 采樣系統(tǒng)和時鐘相位噪聲和抖動的影響。ADI公司Brad Brannon撰寫的應(yīng)用筆記AN-756 。

評論