基于CMOS閾值電壓的基準電路設計

摘要:在數/模混合集成電路設計中電壓基準是重要的模塊之一。針對傳統(tǒng)電路產生的基準電壓易受電源電壓和溫度影響的缺點,提出一種新的設計方案,電路中不使用雙極晶體管,利用PMOS和NMOS的閾值電壓產生兩個獨立于電源電壓和晶體管遷移率的負溫度系數電壓,通過將其相減抵消溫度系數,從而得到任意大小的零溫度系數基準電壓值。該設計方案基于某公司O.5μm CMOS工藝設計,經HSpice仿真驗證表明,各項指標均已達到設計要求。

關鍵詞:CMOS;電壓基準;閾值電壓;溫度系數

電壓基準是混合信號電路設計中一個非常重要的組成單元,它廣泛應用于振蕩器、鎖相環(huán)、穩(wěn)壓器、ADC,DAC等電路中。產生基準的目的是建立一個與工藝和電源電壓無關、不隨溫度變化的直流電壓。目前最常見的實現(xiàn)方式是帶隙(Bandgap)電壓基準,它是利用一個正溫度系數電壓與一個負溫度系數電壓加權求和來獲得零溫度系數的基準電壓。但是,在這種設計中,由于正溫度系數的電壓一般都是通過晶體管的be結壓差得到的,負溫度系數電壓則直接利用晶體管的be 結電壓。由于晶體管固有的溫度特性使其具有以下局限性:

(1)CMOS工藝中對寄生晶體管的參數描述不十分明確;

(2)寄生晶體管基極接地的接法使其只能輸出固定的電壓;

(3)在整個溫度區(qū)間內,由于Vbe和溫度的非線性關系,當需要輸出精確的基準電壓時要進行相應的曲率補償。

為了解決這些問題,提出一種基于CMOS閾值電壓的基準設計方案。它巧妙利用PMOS和NMOS閾值電壓的溫度特性,合成產生與溫度無關的電壓基準,整個電路不使用雙極晶體管,克服了非線性的溫度因子,并能產生任意大小的基準電壓值。

1 傳統(tǒng)帶隙電壓基準電路

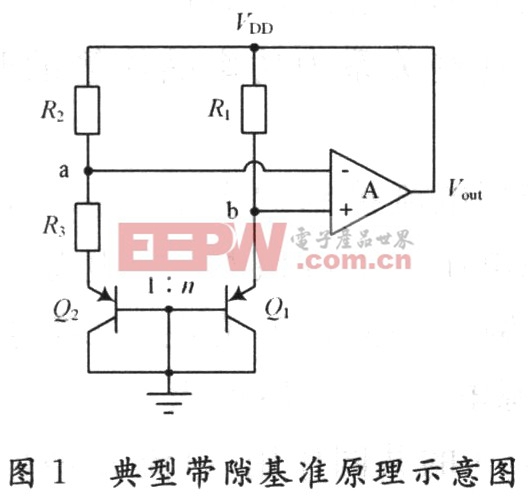

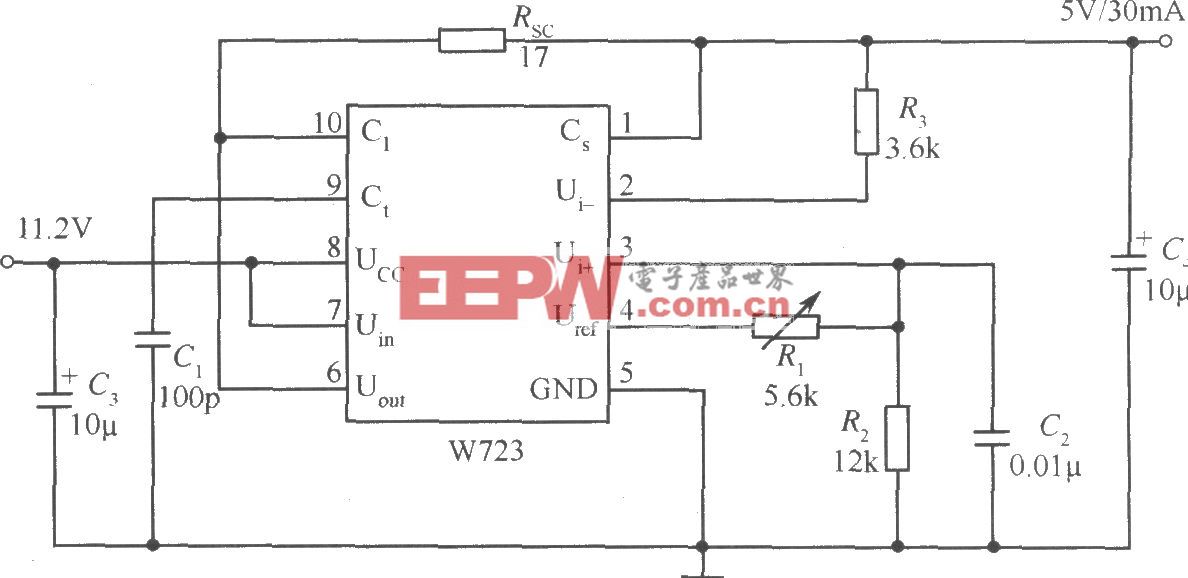

圖1為典型帶隙基準的原理示意圖。

假設R1=R2,根據運算放大器兩輸入端電壓相等的原則,可以得到Va=Vb,又Vbe1-Vbe2=VTlnn,因此輸出電壓為:

![]()

Vbe在室溫下的溫度系數約為-2.0 mV/K,而熱電壓、VT在室溫下的溫度系數約為0.085 mV/K。合理設置R2,R3和n的值,可以得到零溫度系數的基準電壓。

但是,由于前述有關晶體管溫度特性的缺陷,使得實際設計中會存在很多困難。鑒于此,將對傳統(tǒng)帶隙基準進行改進,基于MOS閾值電壓設計一款零溫度系數的基準電路。

2 新型電壓基準電路

2.1 MOS器件的溫度特性

對長溝道MOS器件而言,其工作區(qū)域可劃分為飽和區(qū)和線性區(qū)。

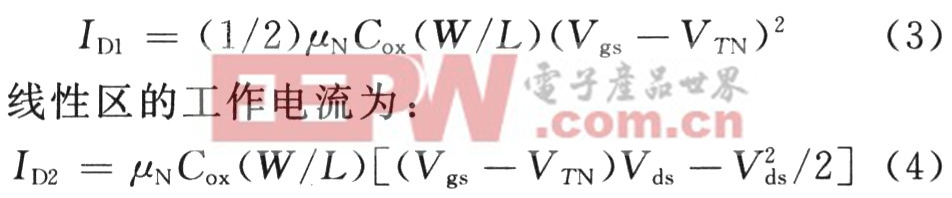

飽和區(qū)的工作電流為:

式中:COX為單位面積的柵電容;pN為電子的遷移率;W,L為柵的寬和長;VTN為NMOS的閾值電壓。在式(3)和式(4)中,有兩項與溫度相關的參數:閾值電壓VTN以及遷移率μN。

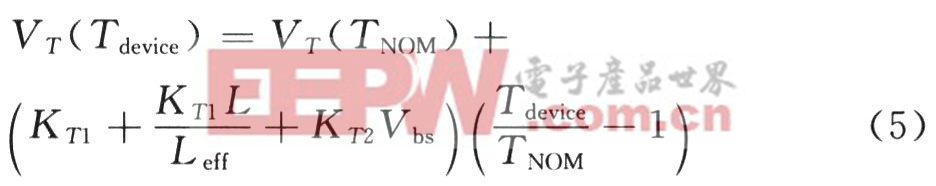

閾值電壓與溫度關系式為:

評論