300MSPS高速10位D/A轉換器AD9751

4 應用設計

4. 1 基準電壓

AD9751內含一個1.2V的帶隙基準電壓。使用內部基準時,在引腳REFIO和ACOM之間接0.1μF的電容可達到去耦的目的。

外部基準可以提供一個固定的基準電壓以提高精度和漂移特性,有時還可以給增益控制提供一個可變的基準電壓,從而起到乘法器的作用。因此,也可以使用接于REFIO端的外部基準。

4.2 鎖相環時鐘

AD9751 的PLL可用來產生用于邊沿觸發鎖存器、多路選擇器以及DAC所必需的內部同步2倍時鐘。PLL電路包括一個相位檢測器、電荷泵、壓控振蕩器(VCO)、輸入數據率范圍控制電路、時鐘邏輯電路和輸入/輸出端控制電路。當使用內部PLL時,RESET接地。而當AD9751處于PLL有效模式時,LOCK作為內部相位檢測器的輸出。當它被鎖定時,該模式下鎖定輸出為邏輯“1”。

表1給出了當PLL有效時,DIV0和DIV1在不同狀態下的輸入時鐘頻率范圍。

表1 PLL有效時DIV0和DIV1不同狀態時的時鐘速率

| CLK頻率 | DIV1 | DIV0 | 范圍控制器 |

| 50MHz~150MHz | 0 | 0 | ÷1 |

| 25MHz~100MHz | 0 | 1 | ÷2 |

| 12.5MHz~50MHz | 1 | 0 | ÷4 |

| 6.25MHz~25MHz | 1 | 1 | ÷8 |

當頻率鎖相環電路的VDD接地時,頻率鎖相環電路將處于無效狀態。此時,外部時鐘必須以合適的DAC輸出更新數據率來驅動CLK的輸入端。存在于輸入端口1和端口2的數據的速率和定時依賴于AD9751是否交替輸入數據,或者僅僅響應單端口上的數據。

當PLL無效時,DIV0和DIV1不再控制PLL,但是它們可被用來控制輸入多路復用器上的數據輸入是交替還是不交替輸入。表2給出了在PLL無效時,DIV0和DIV1在不同組合方式下工作模式。

表2 PLL無效時DIV0,DIV1不同組合時的輸入模式

| 輸入模式 | DIV1 | DIV0 |

| 交替(2x) | 0 | 0 |

| 非交替 | ||

| 端口1選擇 | 0 | 1 |

| 端口2選擇 | 1 | 0 |

| 交替(時鐘增倍器有效) | 1 | 1 |

4.3 模擬輸出

AD9751 有兩個互補的電流輸出端IOUTA和IOUTB,它們可以配置成單端或差分兩種工作模式。IOUTA和IOUTB可通過一個負載電阻RLOAD被轉換成互補的單端電壓輸出VOUTA和VOUTB。而使差分電壓VDIFF存在于VOUTA和VOUTB之間,同時也可以通過一個變壓器或差分放大器來將差分信號轉換成單端電壓。

4.4 數字接口

AD9751 的數字輸入端包括兩個通道,每個通道有10個數據輸入引腳,同時還有一對差分鐘輸入引腳。它的10位并行數據輸入遵循標準的直接二進制編碼形式。DB9為最高有效位(MSB),DB0為最低有效位(LSB)。當所有數據位都為邏輯“1”時,IOUTA產生滿刻度輸出電流。當滿刻度輸出電流在兩個輸出端作為輸入碼元的函數被分離時,IOUTB產生互補輸出。

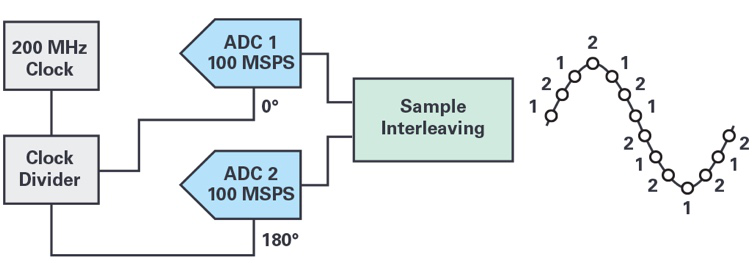

通過使用一個邊沿觸發的主從鎖存器可以實現數字接口。當PLL有效時,或者當使用內部時鐘倍增器時,DAC輸出端在每一個輸入時鐘周期均被更新兩次,其時鐘輸入速率高達150MSPS。這使得DAC的輸出更新率為300MSPS。雖然轉換邊沿的位置可能影響數字饋通和失真特性,但是只要滿足規定的最小倍數,其建立和保持時間就可以在同一時鐘周期內變化。輸入數據在占空比為50%的時鐘下降沿轉變時,可獲得最佳的特性。

AD9751 有一個靈活的差分時鐘輸入端口,采用獨立的電源(如CLKVDD,CLKCOM)可以獲得最優的抖動特性。兩個時鐘輸入端CLK+和CLK-可由單端或差分時鐘源所驅動。對單端工作來說,CLK+應被一個邏輯電源所驅動,而CLK-則應當被設置為邏輯電源的門限電壓。這可以通過如圖2(a)所示的一個電阻分壓器/電容網絡來實現。而對于不同的工作情況,CLK+和CLK-都應當通過一個如圖2(b)所示的電阻分壓網絡被偏置到CLKVDD/2來完成。

因為AD9751的輸出轉換速率高達300MSPS,因此對時鐘和數據輸入信號的要求很嚴。減小減擺率和相應的數字電源電壓(DVDD)可降低數字饋通和芯片上的數字噪聲。

另外,數字信號的路徑也應當盡量短,而且應當與運行長度匹配,以避免傳播延時的不匹配。在AD9751的數字輸入端和驅動器輸出端之間插入一個低值電阻(例如20Ω到100Ω)網絡有助于減小在數字輸入端的任何超調與上升沿,進而減小數字饋通。對于比較長的線路和更高數據率,采用帶狀線技術并增加合適的終端電阻可保持“清潔”的數字輸入端。

評論