基于DDS技術的雜散分析及抑制方法

3.3.1 PLL+DDS頻率合成原理

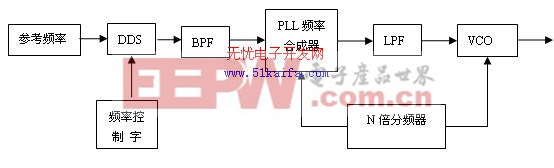

將DDS技術和PLL頻率合成技術結合起來,用一個低頻的DDS源激勵一個PLL系統,用PLL環路將DDS信號倍頻到高頻信號,用濾波器濾除DDS輸出信號雜波干擾,從而使系統同時具有鎖相環技術和DDS技術的優點,使輸出的信號滿足電路的需要。系統組成如圖2所示

圖2

3.3.2 PLL+DDS頻率合成器中的雜散抑制

當DDS源驅動PLL鎖相環時,因為PLL鎖相環相當于一個高Q值的跟蹤濾波器,其帶寬一般不大于100KHz,所以DDS中的大部分雜散會被抑制的很好,從而DDS輸出信號中的雜散偏離主譜線距離大于鎖相環路帶寬的雜散不會惡化。在PLL+DDS系統中,應根據DDS的原理選擇適當的時鐘頻率和輸出信號頻率,使DDS輸出信號與邊端的雜散處于相對理想狀態,從而提高了系統的頻譜純度。

3.3.3 PLL+DDS頻率合成器的實現

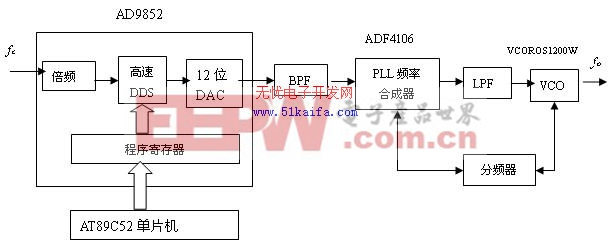

PLL+DDS頻率合成器的組成如圖3所示,下面介紹所選用的主要器件:

1. DDS部分

選用AD公司的AD9852高度集成化芯片,它采用了先進的DDS技術,結合內部高速、高性能D/A 轉換器和比較器,形成可編程、可靈活使用的頻率合成功能。當提供給AD9852精確的頻率時鐘源時,AD9852將產生高穩定、可編程頻率相幅的正弦波。 AD9852使用先進的CMOS技術,使得提供給這個高性能芯片的工作電壓僅為3.3V。

2. PLL合成器部分

PLL合成器部分采用AD公司的ADF4106,它主要由低噪聲數字鑒相器、精確電荷泵、可編程分頻器、可編程A、B計數器及雙模牽制分頻器等部件組成。數字鑒相器用來對R計數器和N計數器的輸出相違進行比較,然后輸出一個與二者相位誤差成比例的誤差電壓。鑒相器內部還有一個可編程的延遲單元,用來控制翻轉脈沖寬度,這個脈沖保證鑒相器傳遞函數沒有死區,因此降低了相位噪聲和引入的雜散。

圖3

4 結束語

直接數字頻率合成(DDS)是一種新型的頻率合成技術,它代表了頻率合成技術數字化發展的新方向。但是,DDS所固有的雜散和噪聲,并且在頻率升高時雜散和噪聲也隨之增加,使它的應用范圍有一定的限制。所以如何減少DDS輸出中的雜散和噪聲成分是當今DDS研究中的核心問題之一。本文所介紹的抖動注入技、平衡DAC結構以及關于ROM幅度表壓縮的幾種算法,都能有效地減少DDS輸出信號中的雜散。尤其當要求得到既有高的頻率分辨率,又有較快的轉換速度和較低噪聲的高頻甚至微波信號時,DDS+PLL技術就顯現出了較強的優越性,經過實際的工程應用,達到了令人滿意的效果。總之,隨著現代科技的不斷發展 DDS的性能會不斷地完善,DDS應用領域也會不斷地拓展。

評論