基于DDS技術的雜散分析及抑制方法

頻率合成技術起源于二十世紀30年代,當時所采用的頻率合成方法是直接頻率合成。它是利用混頻、倍頻、分頻的方法由參考源頻率經過加、減、乘、除運算,直接組合出所需要的的頻率。它的優點是捷變速度快,相位噪聲低,但由于結構復雜,價格昂貴,很快被淘汰。在此之后出現了間接頻率合成。這種方法主要是將相位反饋理論和鎖相環技術運用于頻率合成領域,即所謂的PLL頻率合成技術。PLL頻率合成技術克服了直接式頻率合成的許多缺點,特別是它易于集成化,使得體積小、相位噪聲低、雜散抑制輸出頻率高,但它的頻率切換時間相對較長。隨著數字信號理論和超大規模集成電路的發展,在頻率合成領域誕生了技術性的革命,那就是直接數字頻率合成技術(direct digital synthesis,DDS)。這是一種頻率合成的新方法,頻率轉換時間短、頻率分辨率高、輸出相位連續、控制靈活方便,但其頻率上限較低且雜散較大,極大的限制了DDS的推廣和應用。隨著電子技術的發展,各類電子系統對信號源的要求越來越高,如何抑制DDS輸出信號中雜散也就成了研究熱點。本文給出了幾種抑制雜散的方法,對于運用DDS技術進行工程設計具有一定指導作用。

本文引用地址:http://www.104case.com/article/188610.htm1 DDS的工作原理[1]

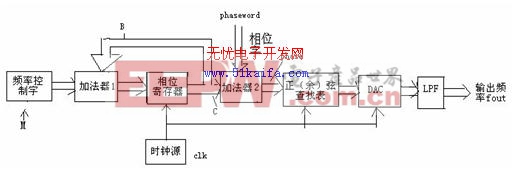

DDS工作結構如圖1所示:

圖1

DDS系統的核心是相位累加器,它由N位加法器與N位相位寄存器構成,類似一個簡單的計數器。每來一個時鐘脈沖,相位寄存器的輸出就增加一個步長的相位增量值,加法器將頻率控制數據與累加寄存器輸出的累加相位數據相加,把相加結果送至累加寄存器的數據輸端。相位累加器進人線性相位累加,累加至滿量時產生一次計數溢出,這個溢出頻率即為DDS的輸出頻率。正弦查詢表是一個可編程只讀存儲器(PROM),存儲的是以相位為地址的一個周期正弦信號的采樣編碼值,包含一個周期正弦波的數字幅度信息。將相位寄存器的輸出與相位控制字相加得到的數據作為一個地址對正弦查詢表進行尋址,查詢表把輸人的地址相位信息映射成正弦波幅度信號,驅動DAC,輸出模擬信號;低通濾波器平滑并濾除不需要的取樣分量,以便輸出頻譜純凈的正弦波信號。

評論