基于DSP Builder的Chirp信號源設(shè)計

1 Chirp函數(shù)的一般特性

電磁波在傳輸過程中,經(jīng)過色散介質(zhì),如不均勻的波導(dǎo),在高空電離層時會發(fā)生色散現(xiàn)象。Chirp函數(shù)在射電天文信號的消色散處理中發(fā)揮著重要的作用,研究在FPGA中實現(xiàn)Chirp函數(shù)是基于FPGA的射電宇宙信號處理的重要組成部分,如圖1所示。

根據(jù)輸出頻率與當(dāng)前采樣時刻對應(yīng)遞變規(guī)律,Chirp函數(shù)一般分線性(Linear)Chirp函數(shù)和非線性(Nonlinear)chirp函數(shù)兩種。圖2,圖3是兩種Chirp函數(shù)在頻域上的表現(xiàn)圖。

從圖2,圖3可以看出,Chirp函數(shù)的頻率輸出與時間關(guān)系f-t關(guān)系可以總結(jié)為:對于線性Chirp函數(shù),在連續(xù)域時間域內(nèi)有關(guān)系式:

![]()

式中:k為常數(shù);f0為初始輸出頻率;t為連續(xù)時間。

在離散時間域有關(guān)系式:

![]()

式中:k為常數(shù);f0為初始輸出頻率;n為采樣點。

對于非線性Chirp函數(shù),在連續(xù)域時間域內(nèi)有關(guān)系式:

![]()

式中:f(t)為非線性函數(shù);f0為初始輸出頻率;t為連續(xù)時間。

在離散時間域有關(guān)系式:

![]()

式中:f(n)為非線性函數(shù);f0為初始輸出頻率;n為采樣點。

2 DDS模塊的設(shè)計

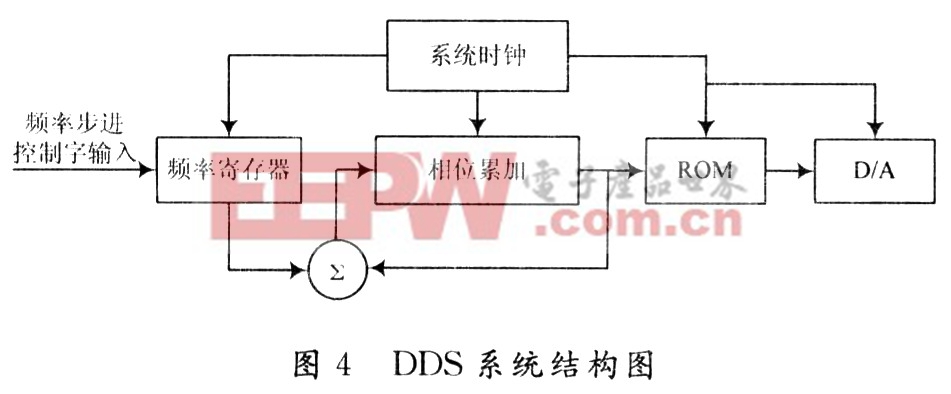

數(shù)字式頻率合成器(DDS)模塊的工作原理是:將0~2π的正弦函數(shù)值分為N份,將各點的幅度值存入ROM中,再用一個相位累加器每次累加相位值ωT,得到當(dāng)前的相位值,通過查找ROM得到當(dāng)前的幅度值,其系統(tǒng)框圖如圖4所示。

DDS的主要參數(shù)包括:系統(tǒng)時鐘頻率、頻率控制字長、頻率分辨率、ROM單元數(shù)、ROM字長。該設(shè)計的DDS是10位的,時鐘頻率為轉(zhuǎn)化為VHDL文件后的輸入時鐘頻率。這是一個很靈活的輸入頻率。在此,假設(shè)輸入頻率為fin,頻率控制字長為16位,ROM單元數(shù)為210,ROM字長為9位,而且頻率分辨率為:

![]()

式中:fc為系統(tǒng)時鐘頻率。

頻率控制字為:

![]()

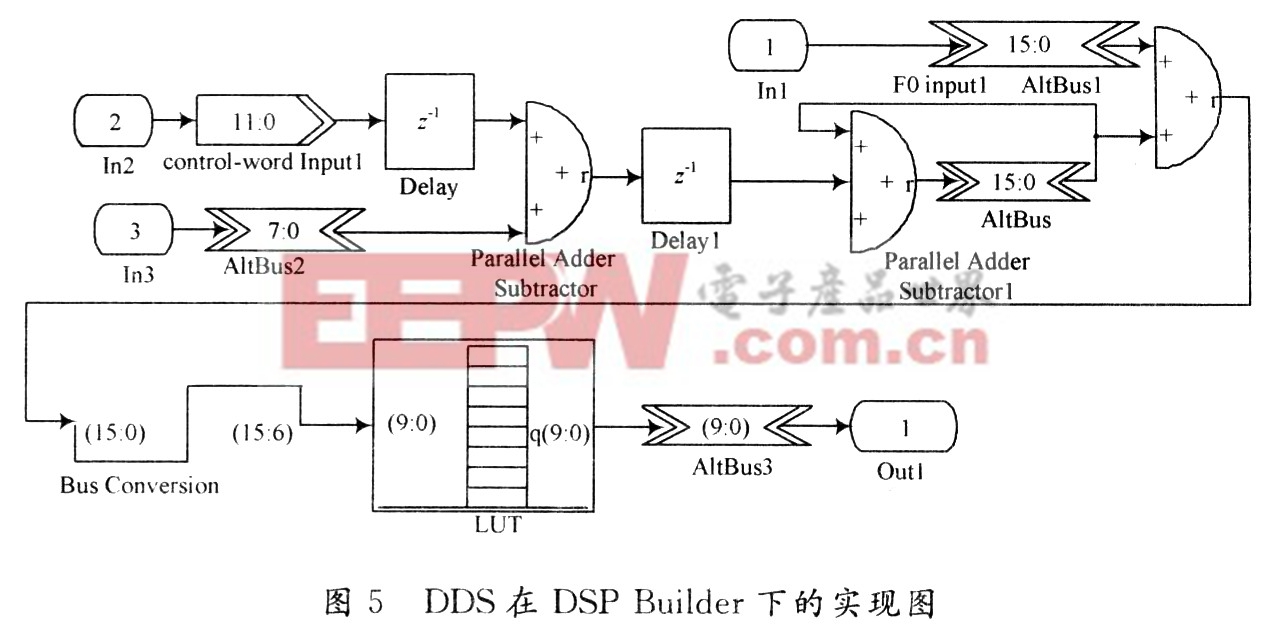

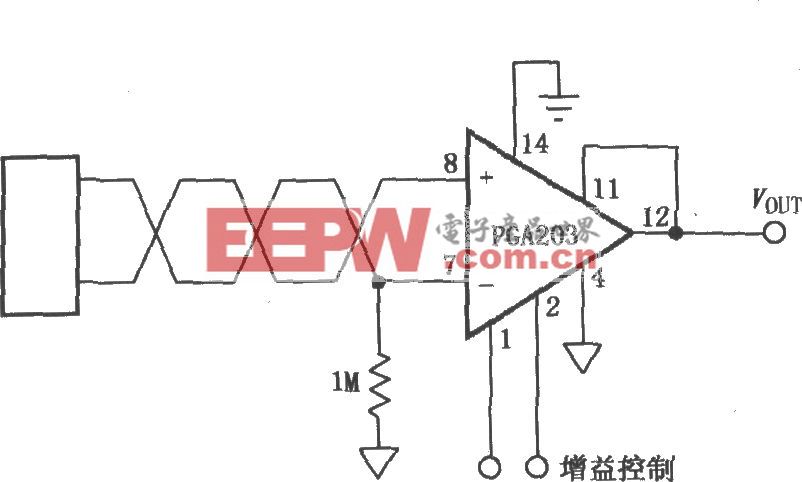

式中:f為要合成的頻率;T為系統(tǒng)時鐘。可見,當(dāng)輸入頻率控制字發(fā)生變化時,輸出頻率fout也發(fā)生相應(yīng)的變化,從DDS到Chirp信號源的設(shè)計就是基于這一思想,如圖5所示。

其中,輸入端口1為初始相位控制字輸入端,它的輸入值決定了信號源的初始輸出相位。輸入口2為頻率控制字FTW輸入端,若在該輸入端寫入不同的頻率控制字值,則可以在輸出端口得到不同的輸出頻率。輸入端口3為初始頻率控制字輸入端,它的輸入值決定了信號源的初始偏置頻率。

LUT為正弦數(shù)據(jù)查找表模塊(Look Up Table)。根據(jù)DSP Builder的算法將一個完整的正弦波周期進(jìn)行1 024次采樣,并存儲于LUT中。在Matlab中設(shè)置Matlab array:511*sin([0:2*pi/(2^10):2*pi]),左邊的輸入端為查找數(shù)據(jù)的地址輸入端,右邊的輸出端為離散正弦波信號輸出端。

第一個并行累加器模塊(Parallel Adder Subtrac-tor)作為相位累加器,采用Altera提供的總線結(jié)構(gòu)(AltBus)模塊決定了該累加器的長度為16位,即該累加器最大可輸出范圍為216,由此決定了公式(5)。

第二個并行累加器模塊(Parallel Adder Subtractor1)作為初相位偏置累加器,將初相位控制字與頻率控制字累加,為輸出頻率提供一個初始偏置相位。

第三個并行累加器模塊(Parallel Addersubtractor 2)作為初始頻率偏置累加器,給輸入的頻率控制字提供一個偏置,是輸出頻率從一個用戶自己可定義的初始頻率開始變換運(yùn)行。

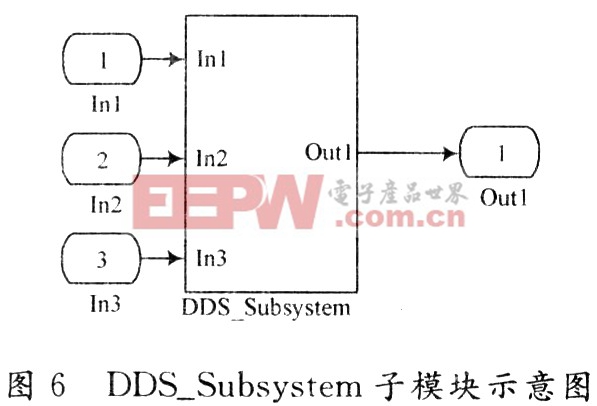

利用總線位寬轉(zhuǎn)換模塊(Bus Conversion)只取出總線信號的高10位,用作驅(qū)動數(shù)據(jù)查找表模塊的地址驅(qū)動信號。為了方便下一步設(shè)計,將圖5封裝成子系統(tǒng)模塊(Subsystem Block),并命名為:DDS_Subsystem,如圖6所示。

圖6中in1為初始相位輸入端,in2為輸入頻率控制字端,in3為初始頻率輸入端。

評論