基于CPLD的異步ASI/SDI信號電復接光傳輸設備的設計

SIGNAL gnd : std_logic := apos;0apos;;

SIGNAL vcc : std_logic := apos;1apos;;

signal N_25 : std_logic;

signal N_12 : std_logic;

signal N_13 : std_logic;

signal N_15 : std_logic;

signal N_16 : std_logic;

signal N_17 : std_logic;

signal N_21 : std_logic;

signal N_22 : std_logic;

signal N_23 : std_logic;

signal N_24 : std_logic;

begin

I30 : G_D Port Map ( CLK=>N_25, D=>N_13, Q=>N_22 );

I29 : G_D Port Map ( CLK=>N_25, D=>N_16, Q=>N_23 );

I34 : G_OUTPUT Port Map ( I=>N_22, O=>Q0 );

I33 : G_OUTPUT Port Map ( I=>N_23, O=>Q1 );

I2 : G_INPUT Port Map ( I=>CLK, O=>N_25 );

I7 : G_INPUT Port Map ( I=>A, O=>N_12 );

I8 : G_INPUT Port Map ( I=>LD, O=>N_21 );

I6 : G_INPUT Port Map ( I=>B, O=>N_15 );

I12 : G_2OR Port Map ( A=>N_17, B=>N_24, Y=>N_16 );

I16 : G_2AND1 Port Map ( AN=>N_21, B=>N_22, Y=>N_24 );

I21 : G_2AND Port Map ( A=>N_21, B=>N_12, Y=>N_13 );

I20 : G_2AND Port Map ( A=>N_21, B=>N_15, Y=>N_17 );

end SCHEMATIC;

architecture SCHEMATIC of 2BS-P is

SIGNAL gnd : std_logic := apos;0apos;;

SIGNAL vcc : std_logic := apos;1apos;;

signal N_5 : std_logic;

signal N_1 : std_logic;

signal N_3 : std_logic;

signal N_4 : std_logic;

begin

I8 : G_OUTPUT Port Map ( I=>N_4, O=>Q0 );

I1 : G_OUTPUT Port Map ( I=>N_5, O=>Q1 );

I2 : G_INPUT Port Map ( I=>CLK, O=>N_3 );

I3 : G_INPUT Port Map ( I=>SIN, O=>N_1 );

I7 : G_D Port Map ( CLK=>N_3, D=>N_4, Q=>N_5 );

I4 : G_D Port Map ( CLK=>N_3, D=>N_1, Q=>N_4 );

end SCHEMATIC;

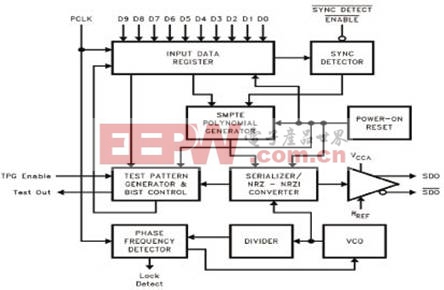

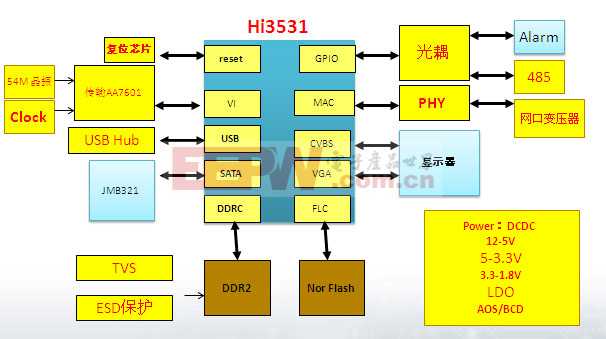

編碼部分電路處理過程如圖8所示。收端光模塊收到數據后,通過CPLD的解復接程序恢復出并行數據和同步時鐘,再通過編碼芯片電路恢復出原始的高速串行信號,經過電纜驅動芯片驅動后最終由傳輸設備輸出,完成整個傳輸過程。其中,編碼電路部分的信號時序如圖9所示。

圖8 編碼部分電路處理過程

圖9 編碼電路信號時序圖

結束語

基于CPLD的異步ASI/SDI信號電復接光傳輸設備的設計使用了最新的ASI/SDI信號電復接/分接技術,可以實現兩路信號的時分復用傳輸,替代了以往以波分復用技術為基礎的多路異步信號傳輸模式,大大節省了生產成本,使產品的市場競爭力進一步提高。

評論