基于FPGA的一種新型8通道數據采集系統

TMS32028335需要完成伺服系統主要的伺服算法工作,其根據算法需要,在適當時刻通過FPGA啟動MAX1300,CS變低,WR變低,數據線和地址線信息寫入FPGA,啟動MAX1300采集數據。當采集工作完成后,對數據進行讀取,CS變低,RD變低,從FPGA讀取數據進行處理,完成伺服算法。

2 FPGA時序控制

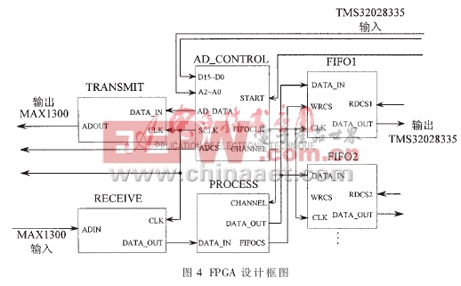

MAX1300正常工作需要32個工作時鐘,而普通MCU或DSP芯片SPI通信端口最大支持16個工作時鐘,使用起來很不方便,因此實際工作中采用FPGA控制MAX1300的工作時序及數據采集,DSP讀取MAX1300采集并經FPGA處理后的數據。FPGA內部時序設計如圖4所示。本文引用地址:http://www.104case.com/article/188312.htm

如圖4所示,FPGA時序設計主要由數據發送模塊TRANSMIT、數據接收模塊RECEIVE、數據處理模塊PROCESS、A/D采集控制模塊AD_CONTROL以及存儲FIFO組成。

實際采集中,AD_CONTROL模塊按DSP要求控制MAX1300時序工作。需要采集數據時,START信號變低后(START連接DSP的WR信號),AD_CONTROL讀取TMS32028335數據線和地址線信息(地址線選擇MAX1300采集通道,數據線加載MAX1300配置數據),并將相應數據AD_DATA寫入TRANSMIT模塊(配置MAX1300,選擇采集通道)。隨后ADCS信號變低,同時SCLK時鐘開始工作,TRANSMIT模塊在SCLK時鐘作用下將數據由ADOUT引腳按位輸出。在采集數據之前先對MAX1300進行配置,選擇電壓范圍以及時鐘工作模式。隨后AD_CONTROL連續輸出32個工作時鐘,在前16個時鐘選擇數據采集通道,后16個時鐘接收MAX1300輸出數據。AD_CONTROL模塊根據地址線高低電平產生通道選擇信號CHANNEL,同時產生內部FIFO工作時鐘FIFOCLK,控制存儲FIFO的讀寫。

評論