測控中高精度快速 A/D 采樣轉換模塊設計

隨著計算機技術的飛速發展和普及,數據采集系統也迅速地得到應用,在生產過程中, 應用這一系統可對生產現場的工藝參數進行采集、監視和記錄,為提高產品質量,降低成 本提供信息和手段。在科學研究中,應用數據采集系統可獲得大量的動態信息,是研究瞬 間物理過程的有力工具,也是獲取科學奧秘的重要手段之一。尤其是在電路測試與診斷過 程中,為了非常詳細、準確地分析電路工作過程中的詳細信息,往往需要采集大量的電路 工作過程中電流、電壓、功耗等信號變化情況,并將這些采集的信號轉換為數字信號以便后臺處理。

本文引用地址:http://www.104case.com/article/188310.htm數據采集的任務,具體地說,就是采集傳感器輸出的模擬信號并轉換成計算機能識別 的數字信號,然后送入計算機或相應的信號處理系統,根據不同需要進行相應的計算和處 理,得出所需的數據;與此同時,將計算機得到的數據進行顯示或打印,以便實現對某些 物理量的監視,其中一部分數據還將被控制生產過程中的計算機控制系統用來控制某些物 理量。在電路測試診斷過程中,在故障未被定位之前,需要采集的大量的信號,并快速進 行分析與處理。因此整個信號采集過程中對采集處理芯片、處理算法的選擇是非常重要的, 直接關系到測試診斷系統的準確性。

2 A/D 芯片的選取與配置

通過增加ADC 采樣位數或提高其采樣頻率,可以有效降低量化噪聲,但由于受工藝等 限制,ADC 的位數限制在一定的范圍內,同時兼顧后續處理器實際處理數據能力,保證采 樣數據實時處理,ADC 的采樣頻率不宜太高,否則采集的數據將無法及時處理。對ADC 采 樣速率和位數的選擇將直接影響著后續微處理器的運算量,因此在本文設計時,必須考慮測 控系統的實時性要求。本系統中微處理器通過中斷讀取A/D 轉換數據,然后進行數字式平 均算法。要在兩次中斷時間間隔內完成如此多的運算,一方面要求處理器的速度要快;另一 方面要求處理時間間隔盡可能長,此可通過適當增加相鄰中斷的間隔時間來實現,即降低 ADC 的采樣速率實現。從提高信噪比的角度考慮,利用過采樣技術,其采樣頻率越高越好; 但從處理器數據處理的實時性角度出發,采樣頻率不宜太高。

本文應用的測控系統中,按照測控需求,每個信號周期內通常采樣 96 個點,采樣值累 加次數為4096 次,若采樣頻率選擇為1 MHZ,則平均每個采樣占用時間為0.393216 秒,為 了滿足測控實時性的要求。因此本系統設計中,ADC 的采樣頻率選擇為1MHZ。

從存儲器存儲數據的角度考慮,為了便于傳輸數據,最后的累加值若利用一個長整形數 據格式(兩個字,共32 位)傳送,實現傳送比較方便,若系統中每點累加次數為4096 次, 則ADC 轉換的位數將不超過20 位(212=4096,32-12=20)。根據測控系統實際精度要 求,并借鑒國內外相關電路經驗,本文設計采用12 位采樣精度即可滿足系統實際要求。

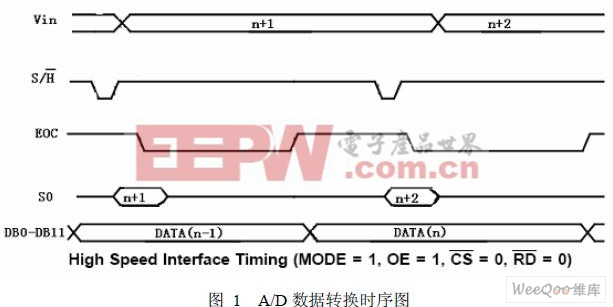

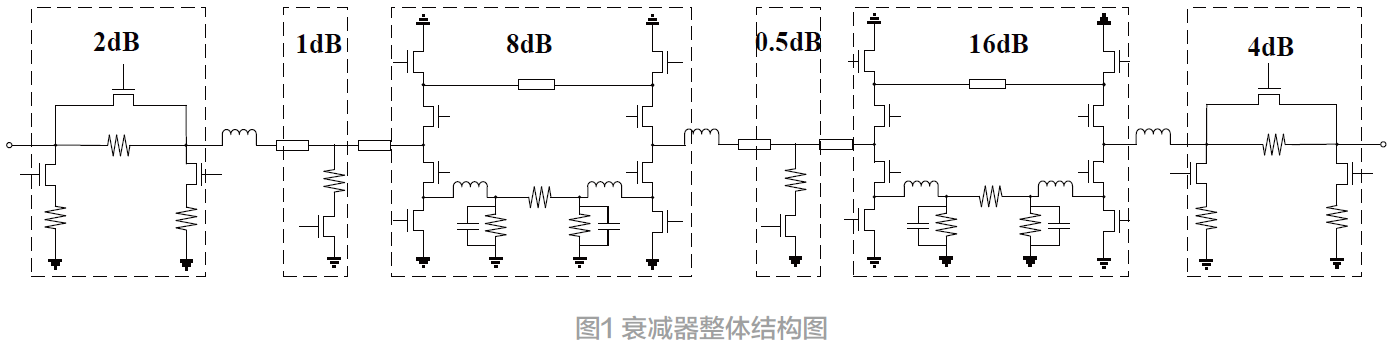

綜合以上諸多考慮,本文的ADC 采用NATIONAL semiconductor 公司的ADC12062,內部 自帶采樣保持電路,12 位采樣精度,最高采樣頻率可達1MHZ,其基準電壓為4.096V,則 最小可檢測電壓為=1mV。ADC12062 采用先進的CMOS 工藝,在高速數據轉換時功耗很 低,其功耗僅為75mW,適合于長時間的穩定工作,特別適合于低功耗要求的便攜式設備。 芯片的A/D 轉換工作時序如圖1 所示。

ADC12062 主要引腳的功能介紹:

ADC IN 模擬信號輸入引腳,其電壓輸入范圍為-0.005DD4.95V。

/CS 片選信號,低電平有效,ADC 處A/D 轉換狀態。

/INI 中斷輸出信號,初始狀態為高電平,當AD 轉換完成以后,變為低電平時,通知微處理器ADC 轉換完成,數據已經在數據線上,可以讀取數據。

/RD 讀控制信號,低電平有效,和同時為低時,可以讀取數據。

S-/H 采樣保持信號,下降沿觸發。該引腳接入控制采樣平臺發出的抽樣觸發脈沖,其下降沿觸發信號取樣。

/PD 低功耗控制模式,高電平時處于正常工作狀態;輸入低電平時,進入低功耗模式。

本A/D 轉換模塊復位以后,ADC 首先處于低功耗狀態,直到處理器發送數據采集命令,控制其處于正常的A/D 轉換工作狀態。

評論