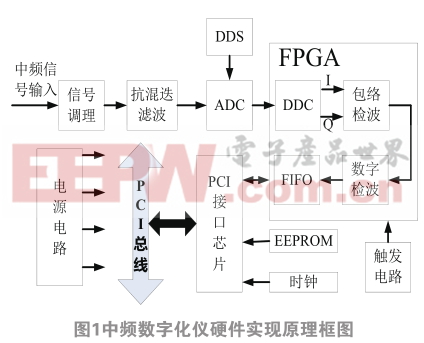

基于DMA的并行數(shù)字信號(hào)高速采集系統(tǒng)

上述方法中,‘5’時(shí)刻至下一周期‘0’時(shí)刻只進(jìn)行了一次寫入,實(shí)際上這段時(shí)間可以容納6個(gè)寫入周期,時(shí)間并沒有被充分地利用。對其進(jìn)一步擴(kuò)展,將系統(tǒng)時(shí)鐘周期充分地利用,可以同時(shí)采集更多通路的信號(hào),將第六到第十個(gè)系統(tǒng)時(shí)鐘周期也用于信號(hào)緩存,則可以同時(shí)緩存16×9=144路數(shù)字信號(hào)。這種情況下,系統(tǒng)的數(shù)據(jù)緩存速率可達(dá)720 Mb/s。

考慮采用SRAM的極限訪問速率的情況,可以選用100 MHz的系統(tǒng)時(shí)鐘,這時(shí)系統(tǒng)的數(shù)據(jù)緩存速率可達(dá)1 520 Mb/s。

選用的SRAM的數(shù)據(jù)寫入極限速率為1 600 Mb/s,此種方法的數(shù)據(jù)緩存速率達(dá)SRAM數(shù)據(jù)緩存極限的95%,實(shí)現(xiàn)了高速的數(shù)據(jù)緩存。

3 緩存數(shù)據(jù)重組織

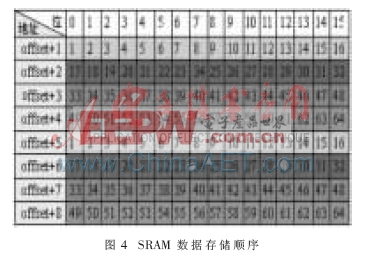

按照上述數(shù)據(jù)緩存的方法,同一通道的數(shù)據(jù)不是連續(xù)地存儲(chǔ)在SRAM中。SRAM中的數(shù)據(jù)存儲(chǔ)順序如圖4所示。圖中第一列表示SRAM地址,offset為數(shù)據(jù)存儲(chǔ)的初始地址偏移;第一行表示數(shù)據(jù)位,選用的SRAM中一個(gè)地址對應(yīng)2字節(jié)數(shù)據(jù),有16個(gè)數(shù)據(jù)位;剩余每個(gè)方格表示一個(gè)數(shù)據(jù)存儲(chǔ)單元,方格里的數(shù)字表示該單元用于存儲(chǔ)第幾通道的數(shù)據(jù)。本文引用地址:http://www.104case.com/article/188156.htm

定位一個(gè)通道的一位數(shù)據(jù)需要知道其對應(yīng)的SRAM地址和位號(hào)。假設(shè)通道m(xù)的第i位數(shù)據(jù)由[addr(m,i),bit(m,i)]定位。分析SRAM中的數(shù)據(jù)存儲(chǔ)順序可知:

addr(m,i)=offset+1+[(m-1)/16]+(i-1)×4;

bit(m,i)=(m-1)%16。

其中m=1,2,3,…,64;i=1,2,3,4,…。

FPGA系統(tǒng)向ARM系統(tǒng)發(fā)送數(shù)據(jù)時(shí),將同一通路的數(shù)據(jù)抽取出來,以一個(gè)字節(jié)為單位連續(xù)發(fā)送,所以需要對存儲(chǔ)的數(shù)據(jù)進(jìn)行重組織。在FPGA系統(tǒng)中,使用6 bit變量dch[5:0]表示通道號(hào),其中000000(b)表示通道1(m=1),000001(b)表示通道2(m=2),依此類推。數(shù)據(jù)位計(jì)數(shù)i使用N位變量bitcnt[N-1:0]來表示,其中N由存儲(chǔ)的總數(shù)據(jù)量決定,與通道號(hào)類似,全零表示i=1情況,1(b)表示i=2情況,依此類推。因而有:

[(m-1)/16]=dch[5:4];

(i-1)×4={bitcnt[N-1:0],00(b)};

(m-1)%16=dch[3:0]。

數(shù)據(jù)由FPGA中的變量定位表示為:

addr=offset+1+{bitcnt[N-1:0],dch[5:4]};

bit=dch[3:0]。

FPGA系統(tǒng)根據(jù)以上公式將各個(gè)通道數(shù)據(jù)逐位地從SRAM中讀出,并移入移位寄存器中,從而把同一通路的數(shù)據(jù)以字節(jié)為單位連續(xù)地組織起來。

4 采集實(shí)驗(yàn)結(jié)果

為了進(jìn)行測試,基于FPGA設(shè)計(jì)了專用信號(hào)發(fā)生器,產(chǎn)生62路數(shù)字信號(hào)用于測試。62路數(shù)字信號(hào)中包括4.07 kHz~520.8 kHz(50 MHz的96分頻)的TTL信號(hào)及恒高、恒低電平信號(hào)。

由于數(shù)字信號(hào)通道數(shù)較多,這里以其中不包含恒高和恒低的9~12通道來說明采集精度,采集結(jié)果如表1。

依此可知,各通道采集結(jié)果與輸入信號(hào)對應(yīng),說明個(gè)通道采集結(jié)果正確,本采集系統(tǒng)可靠。

以某型雷達(dá)做為被測對象,系統(tǒng)進(jìn)行了實(shí)際工作測試。采集性能如表2所示。

本文介紹基于嵌入式技術(shù)的并行數(shù)字信號(hào)采集系統(tǒng)的設(shè)計(jì),系統(tǒng)采用DMA技術(shù)實(shí)現(xiàn)了62路數(shù)字信號(hào)同步采集,用于某型雷達(dá)預(yù)留測試接口信號(hào)的采集,整體采集速率達(dá)310 Ms/s。利用本設(shè)計(jì)中提出的DMA方法,系統(tǒng)可以進(jìn)一步擴(kuò)展,從而實(shí)現(xiàn)128路數(shù)字信號(hào)同步采集,并使整體采集速率達(dá)1 520 Ms/s,此時(shí)SRAM的寫入速度已成為主要的限制。

評論