SoC用低電壓SRAM技術

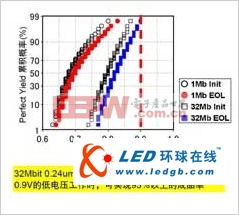

東芝在“2010 Symposium on VLSITechnology”上,發布了采用09年開始量產的40nm工藝SoC的低電壓SRAM技術。該技術為主要用于便攜產品及消費類產品的低功耗工藝技術。通過控制晶體管閾值電壓的經時變化,可抑制SRAM的最小驅動電壓上升。東芝此次證實,單元面積僅為0.24μm2的32MbitSRAM的驅動電壓可在確保95%以上成品率的情況下降至0.9V.因此,低功耗SoC的驅動電壓可從65nm工藝時的1.2V降至0.9V以下。

本文引用地址:http://www.104case.com/article/187892.htm

降低SRAM的電壓是SoC實現微細化時存在的最大技術課題之一。SRAM由于集成尺寸比邏輯部分小的晶體管,因此容易導致每個晶體管的閾值電壓不均。而且,使6個晶體管聯動可實現存儲器功能,因此每個晶體管的不均都容易引發性能不良。所以,尖端SoC“需要以較高的成品率制造大容量且低電壓工作的SRAM的技術”(東芝半導體系統LSI業務部系統LSI元件技術開發部部長親松尚人)。

此次,作為滿足該要求的混載SRAM技術,東芝開發出了不易受NBTI(negative bias temperatureinstability)等導致的閾值電壓變化影響的晶體管技術。NBTI是指晶體管的閾值電壓隨著時間的推移,受印加電壓及溫度的影響發生變化的現象。該公司此次的技術由2個要素構成,分別是(1)控制NBTI發生,(2)控制NBTI等導致的閾值電壓變動對晶體管工作造成的影響。

在確保95%以上成品率的情況下,SRAM的驅動電壓可降至0.9V

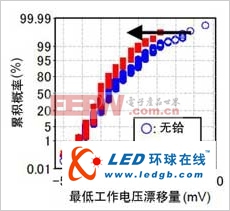

通過向柵極絕緣膜添加Hf,控制NBTI

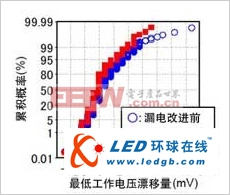

通過改進硅化工藝,控制結漏導致的閾值電壓漂移

(1)作為控制NBTI發生的技術,該公司向多晶硅柵極及SiON柵極絕緣膜的界面附近添加了Hf(鉿)。Hf可作為使SiON柵極絕緣膜與硅底板界面上存在的氧原子懸空鍵(DanglingBond)相互結合的催化劑發揮作用。由此可控制懸空鍵引起的NBTI現象。該技術以東芝與NEC電子(現在的瑞薩電子)的CMOS工藝技術共同開發成果為基礎,于08年開發而成。

(2)為了降低NBTI等導致的閾值電壓變動給晶體管工作造成的影響,該公司使鎳發生了硅化反應,并對其周邊工藝進行了改進。這樣,鎳便會在硅底板中異常擴散,形成結漏電流源,從而控制晶體管的閾值電壓隨著NBTI等發生大幅變動的現象。

東芝采用這些方法在SoC上混載了50M~60Mbit左右的SRAM,而關于DRAM,則采用通過40μm引腳的微焊點(Microbump)使其與SoC芯片層積的方法。東芝已通過部分65nm工藝導入了該方法,今后還打算在40nm工藝上沿用。東芝的親松表示“從DRAM的容量、數據傳輸速度及工藝成本等方面來判斷,尖端工藝最好不要在SoC上混載DRAM”.東芝的目標是“向客戶提供結合最尖端的SoC技術與SiP技術的模塊”.目前DRAM的最大容量約為512Mbit,東芝計劃今后使1Gbit以上的DRAM與SoC實現芯片層積。

評論