基于CSMC工藝的零延時緩沖器的PLL設(shè)計

1 引言

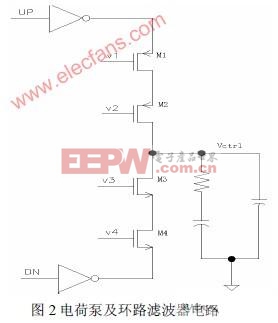

本文引用地址:http://www.104case.com/article/187824.htm本文在傳統(tǒng)鎖相環(huán)結(jié)構(gòu)的基礎(chǔ)上進行改進,設(shè)計了一款用于多路輸出時鐘緩沖器中的鎖相環(huán),其主 要結(jié)構(gòu)包括分頻器、鑒頻鑒相器(PFD)、電荷泵、環(huán)路濾波器和壓控振蕩器(VCO)。在鑒相器前采用預(yù) 分頻結(jié)構(gòu)減小時鐘信號在傳輸過程中受雜散分布的電容電感的影響,避免產(chǎn)生信號畸變、漂移等嚴重影 響電路隨時鐘精確工作的現(xiàn)象。PFD 比較兩個分頻器的信號,產(chǎn)生誤差信號對電荷泵進行充放電,電荷 泵產(chǎn)生的模擬信號經(jīng)過環(huán)路濾波器后調(diào)節(jié)VCO 頻率。VCO 輸出后的分頻器的分頻系數(shù)與預(yù)分頻系數(shù)相 等,目的是使輸出與輸入的時鐘信號頻率相同,起到緩沖而不是分頻的效果。鎖定后實現(xiàn)輸入與輸出信 號零延遲。

2 電路結(jié)構(gòu)

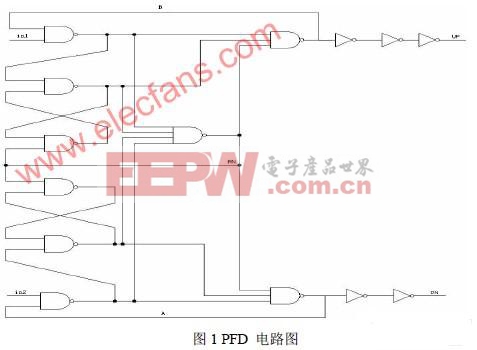

2.1 鑒頻鑒相器(PFD)

PFD 產(chǎn)生關(guān)于頻率和相位誤差的信號,其脈沖寬度與相位誤差成比例的變化,傳輸給電荷泵及環(huán)路 濾波器引起壓控振蕩器控制電壓的變化,進而改變振蕩頻率。電路工作的進程如圖2 所示,這是一個下降沿比較的結(jié)構(gòu),由兩個基本RS 觸發(fā)器和兩個帶復(fù)位端的RS 觸發(fā)器組成。這種鑒相器不僅可以對相位 進行比較,也可以對頻率進行比較,鎖存結(jié)構(gòu)記憶了前一次的輸入信號狀態(tài),從而決定了下一次的輸出 狀態(tài)。

評論