0.6μmCMOS工藝全差分運算放大器的設計

0 引言

本文引用地址:http://www.104case.com/article/187652.htm運算放大器是數據采樣電路中的關鍵部分,如流水線模數轉換器等。在此類設計中,速度和精度是兩個重要因素,而這兩方面的因素都是由運放的各種性能來決定的。

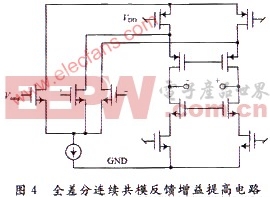

本文設計的帶共模反饋的兩級高增益運算放大器結構分兩級,第一級為套筒式運算放大器,用以達到高增益的目的;第二級采用共源級電路結構,以增大輸出擺幅。另外還引入了共模反饋以提高共模抑制比。該方案不僅從理論上可滿足高增益、高共模抑制比的要求,而且通過了軟件仿真驗證。結果顯示,該結構的直流增益可達到80 dB,相位裕度達到80°,增益帶寬為74 MHz。

1 運放結構

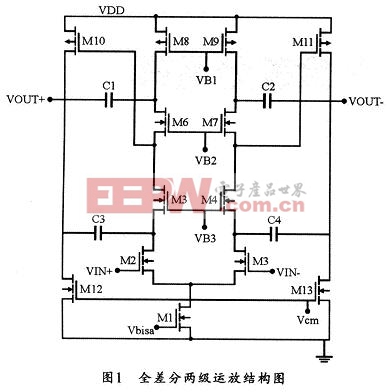

通常所用的運算放大器的結構基本有三種,即簡單兩級運放、折疊共源共柵和套筒式共源共柵。其中兩級結構有大的輸出擺幅,但是頻率特性比較差,一般用米勒補償,可使得相位裕度變小,因而電路的穩定性會變差;套筒式的共源共柵結構,雖然頻率特性較好,又因為它只有兩條主支路,所以功耗比較小。但是這些都是以減小輸入范圍和輸出擺幅為代價的。因此,為了緩解套筒式結構對輸入電壓范圍的限制,本文提出了折疊式運算放大器結構的思路。折疊式結構比套筒式結構有更大的輸入共模電平范圍,但卻以減小增益和帶寬,增大噪聲和功耗為代價的。考慮到折疊共源共柵輸入級結構的功耗比較大,因此,本文選擇套筒式共源共柵結構作為輸入級,最后選擇了如圖1所示的全差分結構的兩級運放結構。

1.1 主運放結構

全差分運算放大電路對環境噪聲具有更強的抑制能力。而套筒式結構則具有高增益、低功耗以及頻率特性好等特點。因此,第一級放大結構(即M0~M8)采用套筒式全差分放大器結構作為輸入級。第二級(即M9~M11)為共源結構,以改善套筒式結構輸出擺幅小的缺點,同時相應提高運算放大器的開環增益。但是,隨著級數的增加,必然會增加電路的零極點,這對系統穩定性的要求更高。因此,必須引入補償電容C3來補償額外的極點,使電路的相位裕度能滿足要求,并使性能穩定。另外,圖1申的VB1用于提供尾電流鏡偏置,VB2和VB3分別用于為PMOS和NMOS提供靜態直流偏置,這三個偏置電壓均提供有偏置電路。

評論