四階連續時間正交帶通ΣΔ調制器的設計

4 電路模塊

ΣΔ調制器中最重要的模塊是構成有源RC積分器和比例加法器的運放, 1 bit量化器和開關電容反饋DAC。

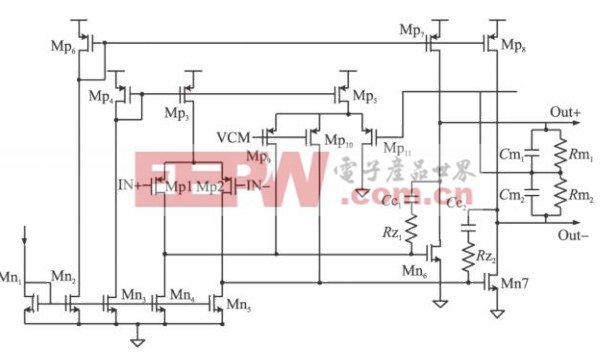

4. 1 運放

ΣΔ調制器中的運放都是兩級米勒結構,如圖5所示。運放第1 級滿足增益和噪聲要求, 采用PMOS作為輸入管可以降低閃爍噪聲;第2級滿足擺幅要求。運放的輸出被共模反饋電路檢測,與參考電壓比較,誤差信號被反饋到運放內部,迫使運放的輸出共模等于參考電平。與米勒電容串聯的電阻用來抵消次極點。

ΣΔ調制器第1級運放直流增益為88 dB,單位增益帶寬為250 MHz,調制器中其余運放的增益為85 dB,單位增益帶寬為45MHz。

圖5 兩級Miller運放

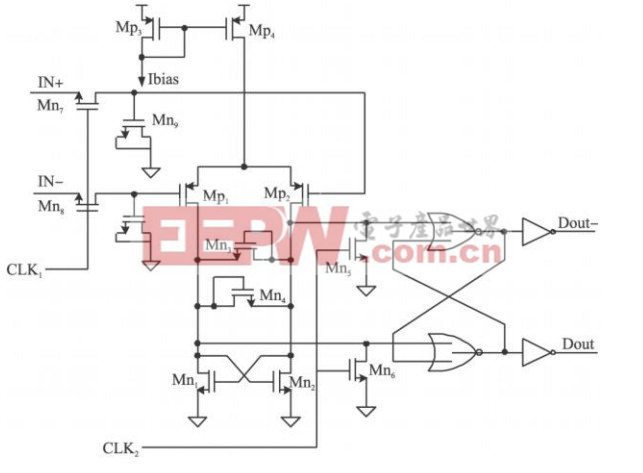

4. 2 量化器

量化器由比較器和SR鎖存器組成,如圖6 所示。比較器由Mp1 和Mp2 構成差分輸入,Mn1 和Mn2 構成的負阻,正的增益起到了再生作用。為了獲得更高的工作速度,在兩個輸出端之間還有兩個二極管連接Mn3 和Mn2 ,對差分輸出端的電壓進行鉗位。當CLK1 和CLK2 為1時,所有開關管閉合,信號被采樣到MOS電容上,比較器的輸出為0,交叉耦合的或非門保持原來邏輯電平不變; 當CLK1和CLK2 為0時,所有開關管截止,比較器的一端產生邏輯電平1,另一段產生邏輯電平0, SR鎖存器更新邏輯值。

圖6 1 bit量化器

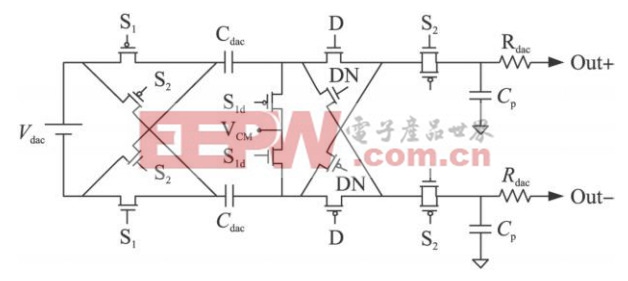

4. 3 開關電容DAC

開關電容DAC由MOS開關,電容和電阻組成,如圖7所示。在第一個時鐘相,開關S1 閉合, S2 斷開,上下電容兩端的電壓為±0. 5Vref。在第二個時鐘相,開關S2 閉合, S1 斷開,電容放電,開關D 和DN決定放電通路。為了減小電荷注入效應,開關S1 比S1d提前閉合。輸出端接第一級運放的輸入,所以在第一個時鐘相開關電容DAC的輸出端電壓等于運放的輸入共模電壓VCM 。

圖7 開關電容DAC

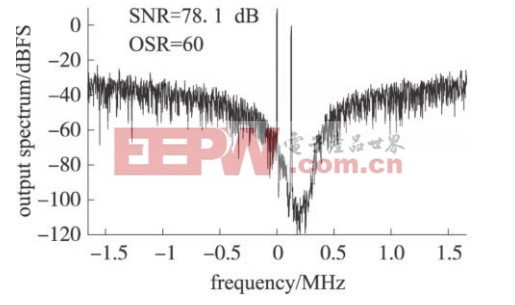

5 仿真結果

四階連續時間正交帶通ΣΔ調制器采用smic0. 13 mixed2signal CMOS工藝實現。采樣頻率為12MHz,過采樣率為60,有效帶寬為200 kHz,中心頻率為200 kHz。用Spectre進行仿真驗證,當I、Q兩路的輸入分別為125 kHz的正弦和余弦信號時,調制器的輸出功率譜密度如圖8所示,整個頻譜近似關于f = 200 kHz對稱,其SNDR為78 dB。

圖8 輸出頻譜密度

6 結論

本文提出了一個基于復數濾波器的四階連續時間帶通ΣΔ調制器電路,非常適用于低中頻架構。

調制器采用開關電容DAC,有效減少了時鐘抖動效應的影響。

評論