提高共源共柵CMOS功率放大器效率的方案

2 功率放大器設計

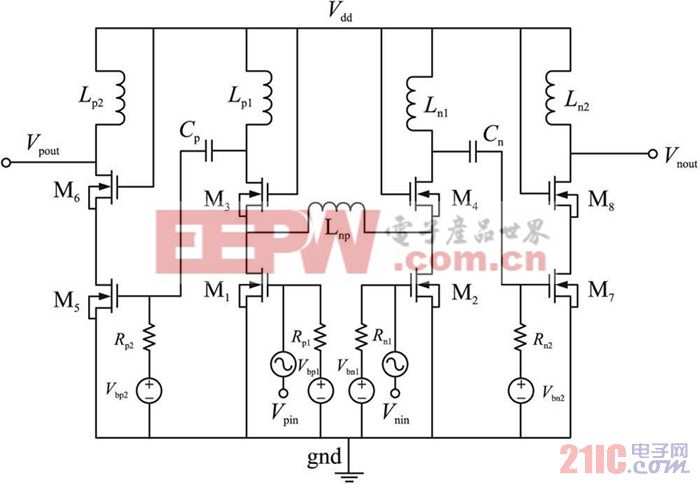

放大電路如圖2所示,電路結構為差分形式,采取兩級放大,分別為驅動級和輸出級。驅動級采用差分的共源共柵(Cascode)結構,可以提供適當的電壓增益;輸出級也是差分的共源共柵結構,在提供一定的電壓增益的同時,還提供輸出功率,這種結構可以提高功放輸出電壓的擺幅,從而降低對MOS管最大電流能力的要求,提高功放的效率。兩級之間采用的耦合電容Cp和Cn在提高隔離度的同時起到級間阻抗匹配的作用。電感Lp1、Lp2、Ln1、Ln2用作負載,電感Lnp用來抵消源極寄生電容對功放效率的影響,其中Lp1、Ln1和Lnp采用工藝庫里的片上螺旋電感來實現,而Lp2和Ln2可以采用高Q值的鍵合線電感實現,這樣可以有效提高功放的增益,當然只要工藝條件允許,在對增益要求不是很高的情況下,也可以采用工藝庫里的片上螺旋電感來實現。單路輸入信號經輸入匹配網絡由巴倫轉換成兩路信號Vpin和Vnin,放大后的兩路信號Vpout和Vnout經輸出匹配網絡由巴倫轉換成一路信號送至天線。其中,輸入匹配采用共軛匹配以達到最大增益,輸出匹配采用功率匹配以輸出最大功率,都是以簡單的LC匹配網絡為實現形式,通過高頻輔助設計軟件ADS中的Smithchart來設計。

圖2 兩級A類放大電路結構示意圖

3 仿真結果

評論