一種新型高速CMOS全差分運算放大器設計

2.2 小信號分析

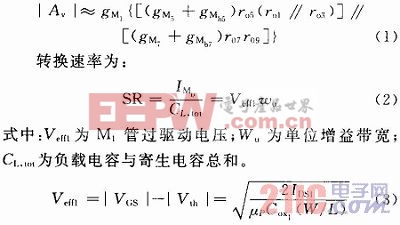

折疊式共源共柵的直流增益為:

2.3 頻率與增益特性分析

單級折疊式共源共柵結構主要有2個極點需要考慮:

在輸出節點處產生主極點:P1=-1/RoutCL;

在折疊點處產生非主極點:P1=-gm5/Cx。

式中Cx為折疊點周圍電容和,且主要取決于CGS7。為使運放能夠穩定工作,需對其進行頻率補償。對于單級運放,由于只有一個主極點,頻率特性較好,在輸出端增加一定的負載電容即可。

由于模擬電路的參數不缺定性,手算的結果在仿真調制時也需要進行適當的修改才能達到預期目標的要求。尾電流的M0以及M9,M10可根據MOS管飽和區電流公式來確定:即,

由式(1)可知,提高增益的方法主要為提高輸入對管M1,M2共源共柵管M5,M6以及M7,M8的跨導。由于MOS管工作電流已經確定,則可通過增加寬長比增加其跨導。但要折衷考慮的是:過多的增加共源共柵管M5,M6的溝道長度會增大次主極點的寄生電容,從而降低次主極點的頻率。所以提高增益的方法主要是增加PMOS管M7,M8的寬長比。而且,M3管與M4管均要流入2條支路的電流,若要減小其對折疊點的電容貢獻,則要求有較高的過驅動電壓。

2.4 直流工作點的確定

由于溝道長度調制作用的存在,MOS管的漏源電壓VDS會對漏源電流IDS產生一定的影響。

有飽和區MOS管漏源電壓與電流間的關系公式:

式中λ為溝道長度調制系數λ∝1/L。在近似漏源電流IDS及過驅動電壓|VGS-Vth|不變的情況下,寬長比W/L與VDS成反比的趨勢。可根據此規律調制每個MOS管的漏源電壓及直流工作點。而進行調制的前提則是每個MOS管都必須工作在飽和區,即滿足VDS>|VGS-Vth|。

2.5 提高轉換速率

轉換是在處理大信號的高速電路中不希望看到的一種非線性現象,大信號的速度被轉換速率限制,原因是對電路中主要電容器充電和放電的電流太小。所以要提高轉換速率。由式(2)可以看出,增大轉換速率的一種方法為提升流過共源共柵管M5,M6的電流,同時減少輸出端補償電容的大小。而電流的增大勢必會提高運放的功耗。而式(3)表明,增大輸入管M1,M2的過驅動電壓也可以提高轉換速率。這樣在電流一定的情況下,器件的寬長比W/L就不能太大,這也許會導致其跨導的減小,因此以上兩種方法均需要折衷號慮。

評論