一種新型高速CMOS全差分運(yùn)算放大器設(shè)計(jì)

摘要:設(shè)計(jì)了一種基于流水線模/數(shù)轉(zhuǎn)換系統(tǒng)應(yīng)用的低壓高速CMOS全差分運(yùn)算放大器。該運(yùn)放采用了折疊式共源共柵放大結(jié)構(gòu)與一種新型連續(xù)時(shí)間共模反饋電路相結(jié)合以達(dá)到高速度及較好的穩(wěn)定性。設(shè)計(jì)基于SMIC 0.25μm CMOS標(biāo)準(zhǔn)工藝模型,在Cadencc環(huán)境下對電路進(jìn)行了Spec tre仿真。在2.5 V單電源電壓下,驅(qū)動(dòng)0.5 pF負(fù)載時(shí),開環(huán)增益為71.1 dB,單位增益帶寬為303 MHz,相位裕度為52°,轉(zhuǎn)換速率高達(dá)368.7 V/μs,建立時(shí)間為12.4 ns。

關(guān)鍵詞:高速運(yùn)算放大器;全差分;折疊式共源共柵;共模反饋

隨著數(shù)/模轉(zhuǎn)換器(DAC)、模/數(shù)轉(zhuǎn)換器(ADC)的廣泛應(yīng)用,高速運(yùn)算放大器作為其核心部件受到越來越廣泛的關(guān)注和研究。速度和精度是模擬集成電路的2個(gè)重要指標(biāo),然而速度的提高取決于運(yùn)放的單位增益帶寬及單極點(diǎn)特性并相互制約,而精度則與運(yùn)放的直流增益密切相關(guān)。在實(shí)際應(yīng)用中需要針對運(yùn)放的特點(diǎn)對這2個(gè)指標(biāo)要進(jìn)行折衷考慮。

1 運(yùn)放結(jié)構(gòu)與選擇

根據(jù)需要,本文設(shè)計(jì)運(yùn)算放大器需要在較低的電壓下能有大的轉(zhuǎn)換速率、快的建立時(shí)間,同時(shí)要折衷考慮增益與頻率特性及共模抑制比(CMRR)和電源抑制比(PSRR)等性能。

常見的用于主運(yùn)放設(shè)計(jì)的結(jié)構(gòu)大致可分3種:兩級式(Two Stage)結(jié)構(gòu)、套簡式共源共柵(Telescopic Cascode)結(jié)構(gòu)及折疊式共源共柵(Fold Cascode)結(jié)構(gòu)。兩級式結(jié)構(gòu)的第1級可提供高的直流增益,而第2級提供大的輸出擺幅。但由于第2級電流很大,故使得運(yùn)放功耗大大增加,同時(shí)由于級聯(lián)而多產(chǎn)生一個(gè)非主極點(diǎn),速度及帶寬都有所降低,需進(jìn)行頻率補(bǔ)償,這樣不僅增加的設(shè)計(jì)復(fù)雜度還會(huì)大大影響運(yùn)放的速度;套簡式共源共柵結(jié)構(gòu)由于只有2條支路,功耗為三者最低,頻率特性最好,但由于需要層疊多級管子,導(dǎo)致輸出擺幅很低,在低電壓工作下很難正常工作,并且輸入輸出端不能短接;而折疊式共源共柵結(jié)構(gòu)的各參數(shù)特性介于前兩者之間,增益基本與套簡式共源共柵相同而低于兩級運(yùn)放,雖為4條支路,功耗及頻率特性均遠(yuǎn)好于兩級運(yùn)放,輸出擺幅大于套筒式共源共柵結(jié)構(gòu),輸入輸出可以短接且輸入共模電平更容易選取并可接近電源供給的一端電壓。經(jīng)綜合考慮,本設(shè)計(jì)采用折疊式共源共柵結(jié)構(gòu)作為主運(yùn)放。

2 主運(yùn)放分析

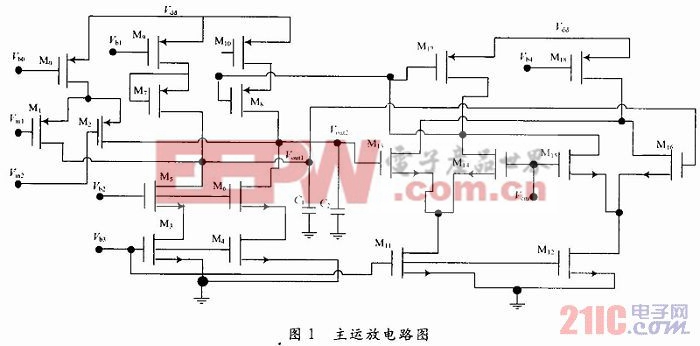

2.1 全差分折疊式共源共柵

全差分運(yùn)放即指輸入和輸出都是差分信號的運(yùn)放,其優(yōu)點(diǎn)為能提供更低的噪聲,較大的輸出電壓擺幅和共模抑制比,可較好地抑制諧波失真的偶數(shù)階項(xiàng)等。雖然NMOS管中載流子遷移率較大,作為輸入器件可達(dá)到更高的增益,但付出的代價(jià)是折疊點(diǎn)上的極點(diǎn)更低而導(dǎo)致相位裕度下降且噪聲更大。綜合考慮,本設(shè)計(jì)采用PMOS管為輸入管的共源共柵結(jié)構(gòu)。如圖1所示,PMOS管M0為偏置電流源,輸入管M1,M2將在M0提供的固定偏置電流作用下,將差分輸入電壓轉(zhuǎn)化為差分電流,經(jīng)過共源共柵管M5,M6的作用下再產(chǎn)生差分輸出電壓Vout1與Vout2。而層疊的PMOS對管M7,M8與M9,M10起到了穩(wěn)定輸出電平與提高增益的作用。

評論