數字電路中△I噪聲的危害分析

1.3 電源電壓波動與時鐘抖動本文引用地址:http://www.104case.com/article/185811.htm

時鐘是數字系統的核心之一。時鐘的產生與分布對系統的性能和功耗都有顯著影響。時鐘偏差(clock skew)和時鐘抖動(clock jitter)[6]是主要問題,它們會導致數字系統的性能下降或工作出錯。然而,電源電壓波動是引起時鐘分布網絡中抖動的主要原因[7]。

從上述分析可見,△I噪聲會引起電源電壓波動。電源電壓波動造成的不良后果是多方面的、是嚴重的。考慮到數字電路的規模越來越大及△I噪聲的疊加性,這一問題會變得更加嚴重。

一個數字系統要求對各個門電路提供穩定的電源電壓。為了確保正常工作,電源電壓的波動應控制在幾百毫伏以內。所以,電源電流尖峰脈沖問題,已成為現代數字設計中必須解決的關鍵問題之一。

2電路內部噪聲

在模擬電路中,外界噪聲通常是關注的重點。而對于數字電路,則內部噪聲最值得關注。一般來說,產生內部噪聲源的原因包括地線噪聲、電源線噪聲、傳輸線(transimission line)反射、串擾(crosstalk)等,其中最重要的噪聲源是地線噪聲和電源線噪聲。

2.1 地線噪聲

由△I噪聲產生過程的分析可知,負載電容CL在放電時引起電流尖峰脈沖,該電流尖峰脈沖流經接地線。由于接地線存在寄生電感,所以電流尖峰脈沖流經接地線時,便產生噪聲電壓,即地線噪聲(接地線還有寄生電阻,但相對于寄生電感引起的噪聲而言,其引起的噪聲要小得多,可以不予考慮)。

實際上,由兩個晶體管同時導通引起的電流尖峰脈沖也流經接地線,但由于相對于負載電容CL放電引起的電流尖峰脈沖而言,該電流尖峰脈沖要弱得多,所以在分析電流尖峰脈沖在接地線上引起的噪聲時,該電流可以不予考慮。

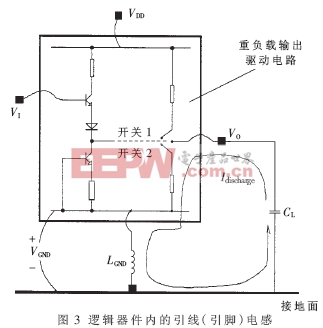

為方便起見,在具體分析地線噪聲的產生與危害時,可將邏輯電路等效為圖3所示的形式。

當開關2 接通時,負載電容CL對地放電。隨著上電壓的下降,其存儲的電荷流向地,在接地回路上形成一個電流尖峰脈沖,記作Idischarge。

隨著放電電流建立然后衰減,這一電流變化通過接地引腳的電感起作用,在器件外的系統地平面與封裝內的地之間感應產生了一個電壓VGND,其大小為:

與滿幅值的輸出電壓相比,VGND通常較小。它不會嚴重影響發送信號,但會嚴重干擾負載,影響對信號的接收。因為對接收電路而言,VGND脈沖就像是直接疊加在輸入信號上的噪聲。

以上是TTL電路的情況。雖然CMOS電路的拓撲(topology)結構不同,但噪聲脈沖的概念是一樣的。

如果同一芯片上的N個容性負載相應的N路輸出同時轉換,則會得到N倍的地電流,于是噪聲脈沖的增大也接近N倍。

評論