模電與數(shù)電:從同一器件的不同應(yīng)用方法看設(shè)計(jì)本質(zhì)

模電與數(shù)電在傳統(tǒng)電子工程中似乎被劃分為兩大領(lǐng)域,然而,它們實(shí)際上是對(duì)同一器件的不同應(yīng)用方法。這種觀念有助于我們理解元器件在各種工作狀態(tài)下的多樣性,并在復(fù)雜的電路設(shè)計(jì)中實(shí)現(xiàn)更高效的系統(tǒng)集成。

本文引用地址:http://www.104case.com/article/202410/464166.htm一、三極管的多重身份:放大器與開關(guān)

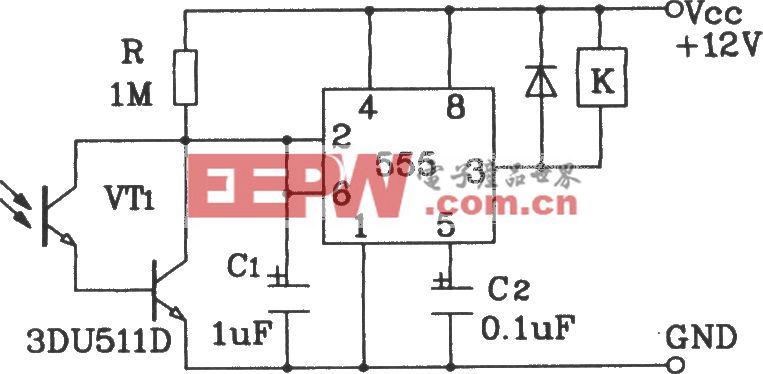

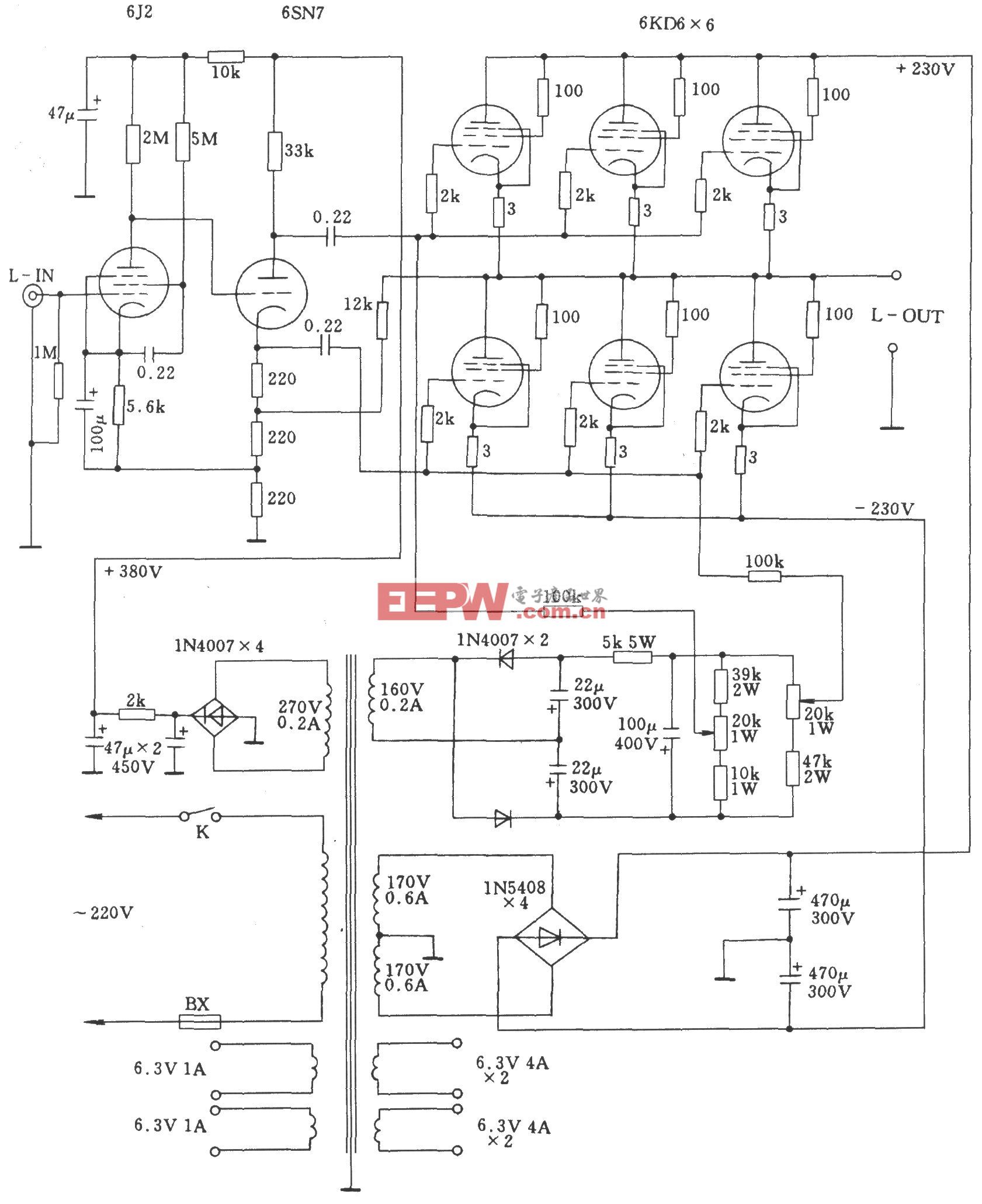

三極管是模擬電路和數(shù)字電路的經(jīng)典實(shí)例。在模擬電路中,三極管工作在放大區(qū),主要用于信號(hào)放大。放大區(qū)設(shè)計(jì)側(cè)重于精確調(diào)節(jié)輸入與輸出的增益、穩(wěn)定性和噪聲特性,通常應(yīng)用于音頻放大器、射頻放大器等對(duì)線性度和信號(hào)保真度有高要求的場(chǎng)合。

然而,當(dāng)三極管工作在截止區(qū)和飽和區(qū)時(shí),就轉(zhuǎn)變成了數(shù)字電路中的開關(guān)。截止和飽和兩個(gè)極端狀態(tài)分別對(duì)應(yīng)著“0”和“1”邏輯值,使三極管成為邏輯門和觸發(fā)器的核心單元。這種開關(guān)功能在高速電路中廣泛應(yīng)用,是實(shí)現(xiàn)邏輯控制、時(shí)序管理等數(shù)字功能的基本手段。

我們把一個(gè)放大電路的放大量提高,輸入是正弦波,輸出原來也是個(gè)正弦波。

我們把放大量調(diào)大,大到正弦波的幅度足夠大,正弦波的波峰和波谷被“削波”,我們發(fā)現(xiàn)輸出的波形從一個(gè)模擬信號(hào),變得像一個(gè)數(shù)字信號(hào)。

我們把示波器調(diào)整一下時(shí)間軸,看著更像。

我們發(fā)現(xiàn)放大量足夠大的時(shí)候,仿佛輸入信號(hào)大于某個(gè)值Vx的時(shí)候,輸出高電平,小于這個(gè)值Vx的時(shí)候,輸出低電平。像極了數(shù)字電路中,電平標(biāo)準(zhǔn)中VT的定義。

削波失真(clipping distortion)的現(xiàn)象:在放大量提高到一定程度時(shí),輸入的正弦波信號(hào)會(huì)超過放大器的線性工作范圍,導(dǎo)致輸出信號(hào)的波峰和波谷被“削去”。這時(shí)候,輸出信號(hào)的波形看起來像一個(gè)方波或脈沖信號(hào),類似于數(shù)字信號(hào)的高低電平。

在這種情況下,放大器相當(dāng)于一個(gè)比較器,當(dāng)輸入信號(hào)超過某個(gè)閾值(例如你提到的Vx)時(shí),輸出為高電平;當(dāng)輸入信號(hào)低于這個(gè)閾值時(shí),輸出為低電平。這與數(shù)字電路中的閾值電壓VT類似,表現(xiàn)出數(shù)字信號(hào)的特性。

在數(shù)字電路中,VT(閾值電壓)是指邏輯門將輸入信號(hào)識(shí)別為高電平(邏輯1)或低電平(邏輯0)的電壓閾值。具體來說:

高電平(邏輯1):輸入電壓高于閾值電壓(VT)時(shí),邏輯門將該信號(hào)識(shí)別為高電平。

低電平(邏輯0):輸入電壓低于閾值電壓(VT)時(shí),邏輯門將該信號(hào)識(shí)別為低電平。

不同類型的邏輯門(如CMOS、TTL等)有不同的閾值電壓,但基本原理相同。閾值電壓是邏輯電路設(shè)計(jì)中一個(gè)關(guān)鍵參數(shù),確保電路能夠可靠地識(shí)別和處理數(shù)字信號(hào)。

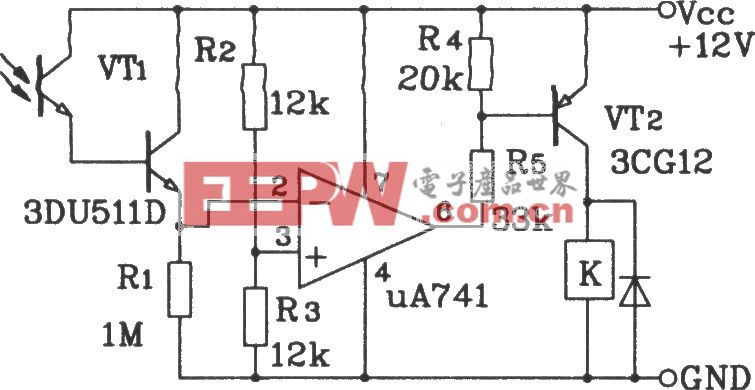

二、運(yùn)算放大器的雙重角色:放大器與比較器

運(yùn)算放大器(運(yùn)放)在模擬與數(shù)字領(lǐng)域之間的跨越更加明顯。作為放大器時(shí),運(yùn)放工作在閉環(huán)狀態(tài),放大并保持輸入信號(hào)的特性,用于濾波、放大、穩(wěn)壓等模擬功能。這種模擬模式下,設(shè)計(jì)者更關(guān)注運(yùn)放的帶寬、增益、失真等參數(shù),以實(shí)現(xiàn)精準(zhǔn)信號(hào)處理。

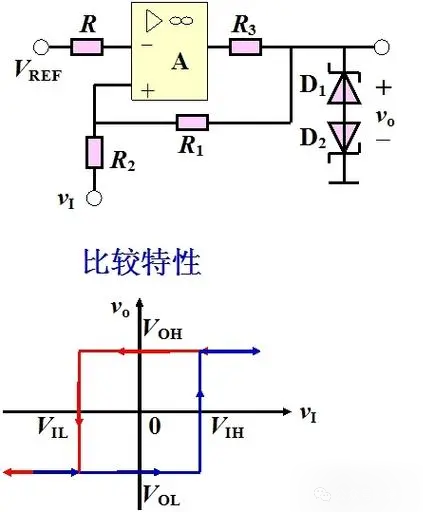

比較器是一種用于比較兩個(gè)電壓信號(hào)的模擬電路,它的輸出只有兩種狀態(tài):高電平或低電平,因此輸出結(jié)果實(shí)際上是一種數(shù)字信號(hào)。這種特性使得比較器在許多應(yīng)用中起到了模擬到數(shù)字轉(zhuǎn)換的作用。下面詳細(xì)解釋比較器的原理及其本質(zhì)。

比較器的基本原理

比較器有兩個(gè)輸入端:正輸入端(V_in+)和負(fù)輸入端(V_in-)。其輸出取決于這兩個(gè)輸入電壓的比較結(jié)果:

當(dāng) V_in+ > V_in- 時(shí),輸出為高電平。

當(dāng) V_in+ < V_in- 時(shí),輸出為低電平。

比較器的內(nèi)部結(jié)構(gòu)與運(yùn)算放大器(Operational Amplifier, Op-Amp)類似,但有一些關(guān)鍵的不同點(diǎn)。比較器通常沒有反饋網(wǎng)絡(luò),因此它的增益非常高,理論上接近無窮大。

而當(dāng)運(yùn)放作為比較器使用時(shí),輸出端不再是連續(xù)的放大信號(hào),而是以高低電平輸出數(shù)字信號(hào)。此時(shí)的運(yùn)放工作在開環(huán)狀態(tài),通過比較輸入信號(hào)與參考電平的大小直接給出二進(jìn)制“高”“低”輸出,成為模數(shù)界面的一個(gè)“數(shù)字化”輸出器件。在很多情況下,設(shè)計(jì)者通過將運(yùn)放的功能轉(zhuǎn)化,實(shí)現(xiàn)在同一電路中切換使用模擬與數(shù)字應(yīng)用。

理想比較器

比較器是一個(gè)開環(huán)或正反饋的理想運(yùn)放。無論輸入電壓大小多少,均被放大到電源電壓。其參數(shù)特點(diǎn)如下:

實(shí)際比較器

電壓比較器的工作特性

比較器的工作過程

輸入電壓比較:比較器的輸入級(jí)比較正輸入電壓(V_in+)和負(fù)輸入電壓(V_in-)。

放大作用:由于比較器的高增益,微小的輸入電壓差異將被放大成一個(gè)明顯的輸出電平變化。

輸出轉(zhuǎn)換:如果正輸入電壓大于負(fù)輸入電壓,輸出將被驅(qū)動(dòng)到高電平(接近電源電壓)。如果正輸入電壓小于負(fù)輸入電壓,輸出將被驅(qū)動(dòng)到低電平(接近地電壓)。

比較器的應(yīng)用

由于其快速響應(yīng)和清晰的輸出狀態(tài),比較器在許多應(yīng)用中非常有用,例如:

電壓監(jiān)測(cè):比較器可以用來監(jiān)測(cè)電壓是否超過某個(gè)閾值,適用于電池充放電管理、電源監(jiān)測(cè)等。

波形生成:在脈沖產(chǎn)生和定時(shí)電路中,比較器可以用來生成方波信號(hào)。

ADC前端:在模數(shù)轉(zhuǎn)換器(ADC)的前端,比較器可以用來將模擬信號(hào)轉(zhuǎn)換為數(shù)字信號(hào)。有的ADC的原理就是N個(gè)比較器。

比較器的本質(zhì)

比較器本質(zhì)上是一種放大倍數(shù)非常高的模擬電路,但其輸出結(jié)果是二進(jìn)制的,這使得它在某種程度上橋接了模擬信號(hào)和數(shù)字信號(hào)的世界。雖然它的內(nèi)部工作原理是模擬的,但它的輸出是數(shù)字的(高電平或低電平),這使得它在數(shù)字電路系統(tǒng)中非常有用。

三、組合邏輯與時(shí)序電路的構(gòu)成關(guān)系

在數(shù)字電路設(shè)計(jì)中,組合邏輯電路和時(shí)序電路構(gòu)成了其基本骨架。組合邏輯電路負(fù)責(zé)瞬時(shí)輸出,直接基于輸入組合的狀態(tài),不依賴于歷史狀態(tài)。通過三極管,可以實(shí)現(xiàn)基本的邏輯門(如與門、或門和非門),從而構(gòu)建加法器、比較器等邏輯功能塊。

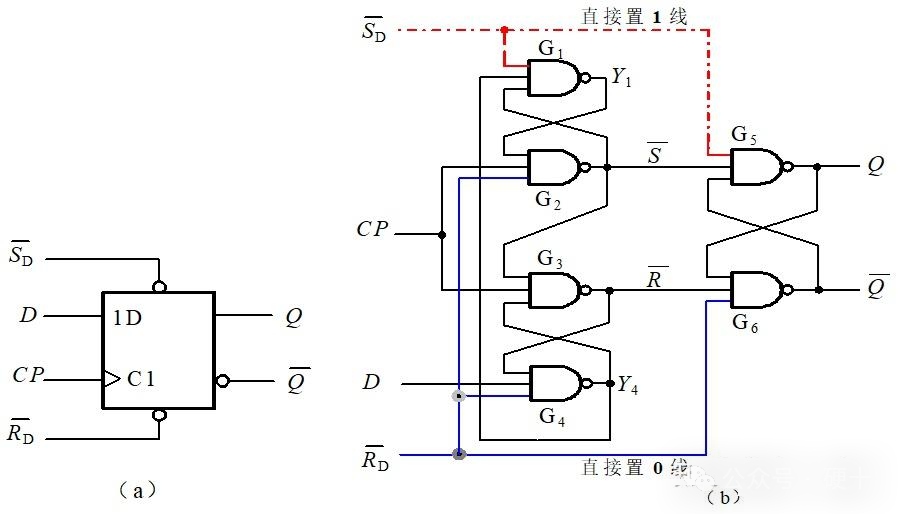

晶體管或者場(chǎng)效應(yīng)管組成了組合邏輯,組合邏輯電路組合形成了觸發(fā)器電路。觸發(fā)器電路和組合邏輯電路共同組合形成了各種集成電路器件。

時(shí)序電路則是在組合邏輯的基礎(chǔ)上增加了存儲(chǔ)元素,如觸發(fā)器等,使電路能夠記住之前的狀態(tài),從而在下一個(gè)時(shí)鐘周期內(nèi)繼續(xù)發(fā)揮作用。時(shí)序電路在數(shù)字電路中的作用至關(guān)重要,是構(gòu)成計(jì)數(shù)器、寄存器等存儲(chǔ)設(shè)備的基礎(chǔ),也是所有時(shí)鐘同步電路的核心。

因此,數(shù)字電路的構(gòu)建離不開組合邏輯和時(shí)序電路的配合。組合邏輯電路處理即時(shí)數(shù)據(jù),而時(shí)序電路保存狀態(tài)和實(shí)現(xiàn)時(shí)鐘控制,這種結(jié)構(gòu)使數(shù)字電路在處理速度和數(shù)據(jù)存儲(chǔ)方面均能滿足復(fù)雜應(yīng)用的需求。

四、ADC的橋梁作用:模擬到數(shù)字的轉(zhuǎn)換

模數(shù)轉(zhuǎn)換器(ADC)在現(xiàn)代電子系統(tǒng)中扮演著連接模擬與數(shù)字世界的關(guān)鍵角色。ADC將連續(xù)的模擬信號(hào)采樣、量化并轉(zhuǎn)換成離散的數(shù)字信號(hào),使得模擬信號(hào)能在數(shù)字電路中處理、存儲(chǔ)和傳輸。ADC的分辨率和采樣速率等性能直接決定了轉(zhuǎn)換精度和信號(hào)的還原度,適合不同的應(yīng)用需求。

在傳感器應(yīng)用中,例如溫度傳感器、壓力傳感器和加速度計(jì)等,ADC通過將傳感器輸出的模擬信號(hào)轉(zhuǎn)換為數(shù)字信號(hào),使其能夠與微控制器和DSP等數(shù)字處理器無縫集成。這種集成不僅提高了數(shù)據(jù)處理的靈活性,還使得系統(tǒng)能夠在數(shù)字域?qū)崿F(xiàn)高效的濾波、運(yùn)算和控制功能。

五、高速數(shù)字信號(hào)的模擬分析:信號(hào)完整性與亞穩(wěn)態(tài)

在分析數(shù)字電路的高速信號(hào)完整性時(shí),模擬電路的分析方法同樣具有重要意義。例如,在處理高速信號(hào)時(shí),信號(hào)的波形完整性往往會(huì)受到寄生電容、電感等因素的干擾,導(dǎo)致信號(hào)失真。信號(hào)完整性分析將數(shù)字信號(hào)作為一種模擬波形來研究,關(guān)注信號(hào)在傳輸路徑上的阻抗匹配、反射、串?dāng)_等問題。

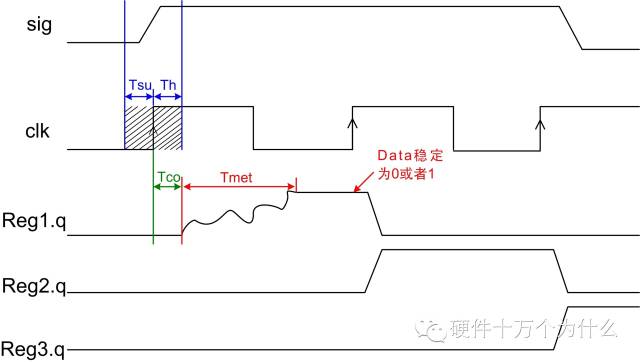

另一個(gè)典型案例是亞穩(wěn)態(tài)(metastability)。在數(shù)字電路中,亞穩(wěn)態(tài)指的是由于信號(hào)傳輸延遲或觸發(fā)器時(shí)序不匹配而導(dǎo)致輸出處于不確定的中間狀態(tài)。盡管亞穩(wěn)態(tài)本質(zhì)上是一個(gè)數(shù)字現(xiàn)象,但它的形成、維持和消退卻都依賴于模擬電路理論。通過對(duì)模擬特性的分析,設(shè)計(jì)者可以識(shí)別并避免亞穩(wěn)態(tài)對(duì)數(shù)字系統(tǒng)造成的不良影響。

亞穩(wěn)態(tài)

在數(shù)字電路中,亞穩(wěn)態(tài)(metastability)是指在某些條件下,電路不能迅速且可靠地確定輸出狀態(tài)的情況。亞穩(wěn)態(tài)通常發(fā)生在時(shí)序電路中,尤其是在異步信號(hào)交互或時(shí)鐘邊沿較近的情況下。以下是關(guān)于亞穩(wěn)態(tài)的詳細(xì)解釋:

原因

亞穩(wěn)態(tài)主要發(fā)生在觸發(fā)器(如D觸發(fā)器)或鎖存器中,當(dāng)輸入信號(hào)在時(shí)鐘上升沿或下降沿附近發(fā)生變化時(shí),電路可能無法及時(shí)做出明確的高低電平判斷,進(jìn)入一種不穩(wěn)定的中間狀態(tài)。

表現(xiàn)

當(dāng)電路進(jìn)入亞穩(wěn)態(tài)時(shí),輸出信號(hào)可能會(huì)在一定時(shí)間內(nèi)保持在一個(gè)不確定的電壓范圍內(nèi),而不是明確的高電平或低電平。這種不確定性可能會(huì)傳遞到后續(xù)的邏輯電路,導(dǎo)致系統(tǒng)錯(cuò)誤。

解決方案

同步設(shè)計(jì):盡量在同一個(gè)時(shí)鐘域內(nèi)設(shè)計(jì)電路,減少異步信號(hào)的交互。

多級(jí)同步器:使用多級(jí)觸發(fā)器將異步信號(hào)同步到系統(tǒng)時(shí)鐘,以減少亞穩(wěn)態(tài)的概率。

提高時(shí)鐘頻率或設(shè)置更長(zhǎng)的時(shí)序裕量:確保信號(hào)有足夠的時(shí)間穩(wěn)定在時(shí)鐘邊沿前后。

結(jié)合VT和亞穩(wěn)態(tài)的解釋

在數(shù)字電路中,閾值電壓(VT)和亞穩(wěn)態(tài)有著密切的關(guān)系。當(dāng)輸入信號(hào)在VT附近變化且時(shí)序條件不滿足時(shí),電路容易進(jìn)入亞穩(wěn)態(tài)。這種情況下,電路不能確定輸入信號(hào)是否已經(jīng)跨越了閾值電壓,從而導(dǎo)致輸出信號(hào)不穩(wěn)定。因此,設(shè)計(jì)可靠的數(shù)字電路時(shí),不僅要考慮閾值電壓的設(shè)置,還需要關(guān)注時(shí)序約束和信號(hào)同步問題,以減少亞穩(wěn)態(tài)發(fā)生的概率。

總之,閾值電壓是決定數(shù)字電路輸入信號(hào)識(shí)別的重要參數(shù),而亞穩(wěn)態(tài)則是數(shù)字電路在某些條件下無法迅速確定輸出狀態(tài)的現(xiàn)象。通過合理設(shè)計(jì),可以在確保電路可靠性的同時(shí),減少亞穩(wěn)態(tài)的發(fā)生。

這種現(xiàn)象可以用示波器來觀察,當(dāng)你調(diào)整時(shí)間軸時(shí),可以更清楚地看到輸出信號(hào)的方波形態(tài),進(jìn)一步驗(yàn)證了你的觀察。這種模擬信號(hào)轉(zhuǎn)變?yōu)閿?shù)字信號(hào)的過程在某些應(yīng)用中是有用的,例如信號(hào)處理和數(shù)據(jù)轉(zhuǎn)換。

總結(jié)起來,放大量足夠大時(shí),放大器輸出信號(hào)的削波現(xiàn)象使得它具備了類似于數(shù)字電路的特性,將輸入的模擬信號(hào)轉(zhuǎn)換為具有高低電平的數(shù)字信號(hào)。

將模電與數(shù)電視作同一器件在不同應(yīng)用場(chǎng)景下的兩種方式,不僅拓寬了設(shè)計(jì)思維,也讓我們?cè)趯?shí)際設(shè)計(jì)中更加靈活。模電與數(shù)電的交叉融合不僅推動(dòng)了現(xiàn)代電子技術(shù)的發(fā)展,也賦予了元器件新的生命力,使其在各種復(fù)雜系統(tǒng)中發(fā)揮最大潛力。

評(píng)論