FPGA攻略之Testbench篇

上述兩種代碼的目的基本都是延時(shí)復(fù)位,但一個(gè)異步復(fù)位,一個(gè)同步復(fù)位,用途不同,小朱同學(xué)一般使用異步復(fù)位。

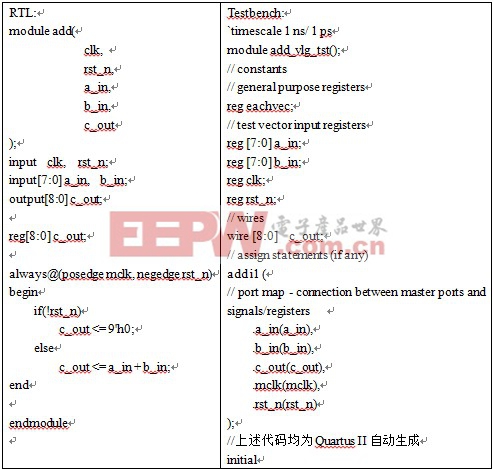

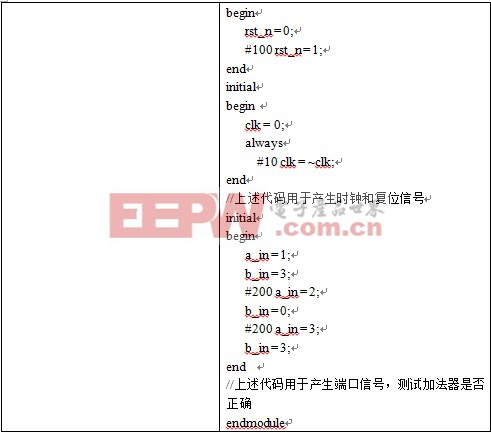

本文引用地址:http://www.104case.com/article/184677.htm最后“判斷被測(cè)試設(shè)計(jì)的輸出相應(yīng)是否滿足設(shè)計(jì)要求”。首先介紹最常用的兩個(gè)系統(tǒng)任務(wù)函數(shù)$stop和$finish。$stop代表暫停仿真后返回軟件操作主窗口,將控制權(quán)交給user;$finish代表終止仿真后關(guān)閉軟件操作主窗口。其他任務(wù)函數(shù)如$monitor、$display 、$time、$fwrite等也比較重要,用到的時(shí)候再一一介紹。為直觀介紹,使用一個(gè)例程來(lái)描述,下面是加法器的RTL代碼及Testbench:

注意了clk、rst_n后,其他端口根據(jù)需要相應(yīng)加測(cè)試信號(hào)即可,然后把RTL代碼及Testbench添加到Modelsim仿真觀察輸出波形等,以驗(yàn)證RTL代碼的正確與否,若與預(yù)期相符則驗(yàn)證結(jié)束,反之則修改代碼至與預(yù)期相符。

好了,Testbench就寫(xiě)到這里,但沒(méi)有結(jié)束,實(shí)踐是檢驗(yàn)真理的唯一標(biāo)準(zhǔn),下一篇將結(jié)合Modelsim,以可視化的方式繼續(xù)探討Testbench,深入了解仿真的意義。

fpga相關(guān)文章:fpga是什么

評(píng)論