高速電路設計中信號完整性分析

在高速電路設計中,對信號布線存在的另一個共性問題。如果沒有特別的原因,應該盡可能消除所有的短接線。在高頻率電路設計中,短接線就如同由于信號線的阻抗匹配而引發的輻射一樣。

在高速電路設計的布線中特別需要注意差分對的布線。差分對是通過兩條完全互補信號線驅動的。差分對可以很好的避免噪聲干擾和改進S/N率。然而差分對信號線對布線有特別高的要求:

1、兩條線必須盡可能靠近布線;

2、兩條線必須長度完全一致;

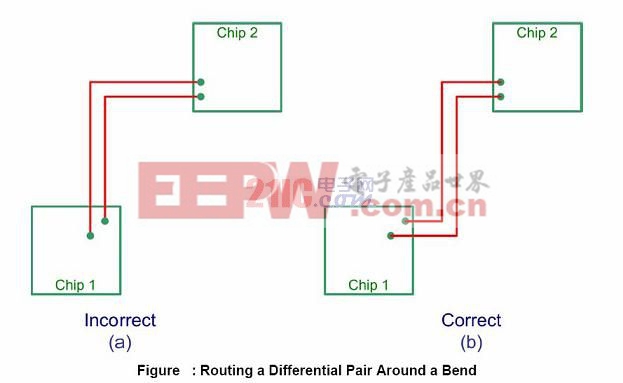

在兩個沒排列在一起的器件間布差分對信號線如何合理的布線是一個關鍵問題。

上圖a中由于兩條信號線的長度不一致,將會出現一些不確定風險。正確的布線應采取上圖b中的方式。在差分對布線中的通用規則是:保持兩條信號線同等間距并相互靠近。

5、串擾

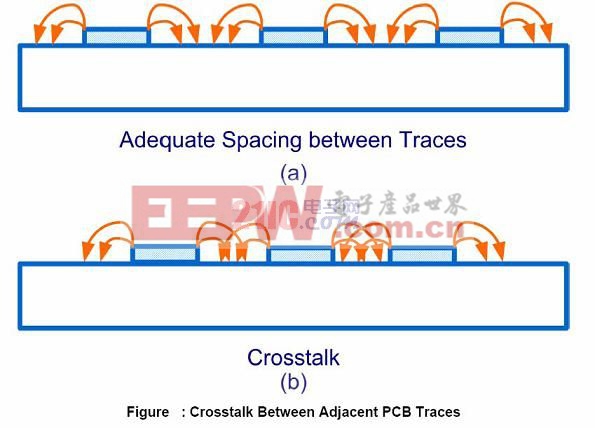

在PCB設計中,串擾問題是另一個值得關注的問題。下圖中顯示出在一個PCB中相鄰的三對并排信號線間的串擾區域及關聯的電磁區。當信號線間的間隔太小時,信號線間的電磁區將相互影響,從而導致信號的惡化,這就是串擾。

電度表相關文章:電度表原理

評論