高速電路設計中信號完整性分析

2、阻抗、反射及終端匹配本文引用地址:http://www.104case.com/article/181028.htm

阻抗控制和終端匹配是高速電路設計中的基本問題。通常每個電路設計中射頻電路均被認為是最重要的部分,然而一些比射頻更高頻率的數字電路設計反而忽視了阻抗和終端匹配。

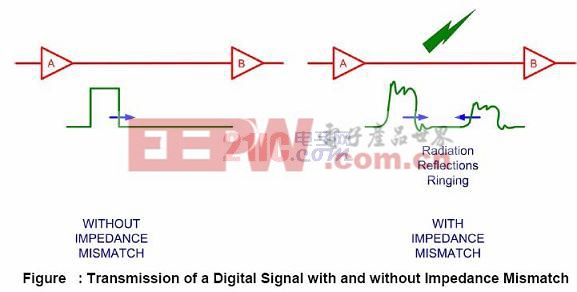

由于阻抗失配產生的幾種對數字電路致命的影響,參見下圖:

a.數字信號將會在接收設備輸入端和發射設備的輸出端間造成反射。反射信號被彈回并且沿著線的兩端傳播直到最后被完全吸收。

b.反射信號造成信號在通過傳輸線的響鈴效應,響鈴將影響電壓和信號時延和信號的完全惡化。

c.失配信號路徑可能導致信號對環境的輻射。

由阻抗不匹配引起的問題可以通過終端電阻降到最小。終端電阻通常是在靠近接收端的信號線上放置一到兩個分立器件,簡單的做法就是串接小的電阻。

終端電阻限制了信號上升時間及吸收了部分反射的能量。值得注意的是利用阻抗匹配并不能完全消除破壞性因素。然而認真的選用合適的器件,終端阻抗可以很有效的控制信號的完整性。

并不是所有的信號線都需要阻抗控制,在一些諸如緊湊型 PCI 規格要求中的特征阻抗和終端阻抗特性。

對于別的沒有阻抗控制規范要求的其他標準以及設計者并沒有特意關注的。最終的標準可能發生變化從一個應用到另一個應用中。因此需要考慮信號線的長度(相關與延遲Td)以及信號上升時間(Tr)。通用的對阻抗控制規則是Td(延遲)應大于Tr的1/6。

3、內電層及內電層分割

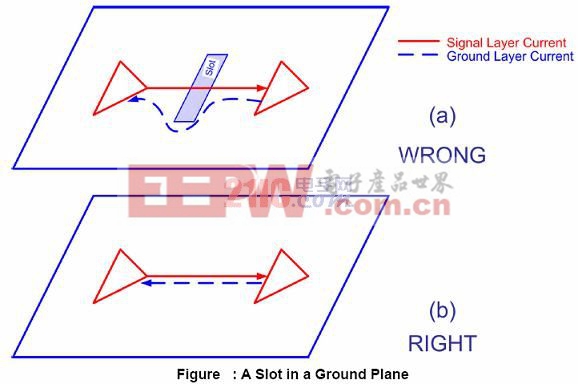

在電流環路設計中會被數字電路設計者忽視的因素,包括對單端信號在兩個門電路間傳送的考慮(如下圖)。從門A 流向門B的電流環路,然后再從地平面返回到門A。

電度表相關文章:電度表原理

評論