基于TMS320F2812的最小系統設計

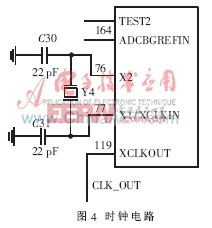

1.3時鐘電路

鎖向環(PLL)模塊主要用來控制DSP 內核的工作頻率,外部提供一個參考時鐘輸入,經過PLL倍頻或分頻后提供給DSP 內核。本系統采用基于PLL的晶體工作模式,通過外部無源晶體為芯片提供時鐘基準,本文所選用的外部晶振是30 MHz。具體電路如圖4所示。本文引用地址:http://www.104case.com/article/180693.htm

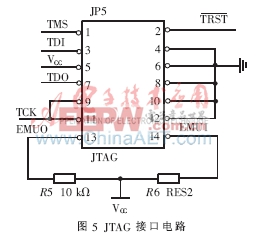

1.4 JTAG接口電路

JTAG接口提供對DSP內部Flash的燒寫和仿真調試,它所具備的這些能力需要軟件的配合,具體實現功能則由具體的軟件決定。JTAG接口是一個業界標準,這部分的引腳定義不要隨意改變。本設計中將其設計成一個標準的14針插座,可以供仿真器調試目標板。具體的連接如圖5所示。

1.5外部接口電路

為了方便擴展及二次開發,將TMS320F2812的4個方向的各個主要引腳全部引出。采用4個30針的雙排針腳式接口將120個重要的引腳引出,可以分配給地址線、數據線、AD模塊和時鐘電源等。在這里,具體的引腳外接就不再詳述了,只介紹幾個常用的外擴模塊電路。當然,在對最小系統的利用時,可以增加相應的模塊來完成特定的功能,例如可以增加RS-485通信電路,在擴展的同時要注意用DC-DC進行物理隔離,尤其在工業應用場合。

1.5.1 外擴RAM電路和外擴Flash電路

為了增加系統的程序存儲空間,提高系統的工作效率,根據設計要求外擴了Flash電路和RAM電路。選用的RAM 型號為IS61LV25616AL,256 KB×16 bit大小。這里用了A0~A17共18根地址線,最大為256 KB;D0~D15 共16 根數據線。片選CS6和讀寫WR、RD 信號都由DSP引出。外擴的Flash型號為SST39VF800,512 KB×16 bit,方便用戶燒寫較大程序。本文比SRAM多了1根地址線,所以最大可以達到512 KB,片選信號用CS2。具體連接如圖6所示。

評論