基于位線循環(huán)充電SRAM模式的自定時(shí)電路設(shè)計(jì)

HBLSA-SRAM不僅可以降低位線的電壓擺幅,還可以有效地減小位線的電容負(fù)載。位線的負(fù)載電容很大程度上取決于位線上連接的MOS管數(shù)量。如圖1所示,在每一個(gè)Group中有M個(gè)存儲(chǔ)單元,而一共有N個(gè)Group,所以總共有M×N個(gè)存儲(chǔ)單元。對于一個(gè)傳統(tǒng)的SRAM結(jié)構(gòu)有如此的容量,那么其位線上一共會(huì)接M×N個(gè)MOS管。但對于HBLSA-SRAM來說,將連接到主位線和局部位線的MOS管加在一起也不過N+M+5個(gè)。其中,對于主位線一共連接N個(gè)MOS管,而局部位線一共連接M+5個(gè)MOS管,M為M個(gè)存儲(chǔ)單元的傳輸管,有1個(gè)來自與主位線連接的MOS管,另外4個(gè)來自局部的靈敏放大器。所以,不但位線擺幅顯著下降,而且位線電容負(fù)載也下降了。

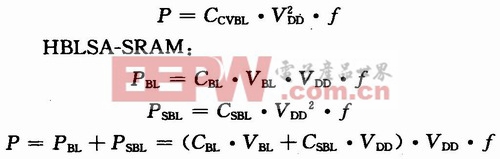

HBLSA-SRAM的讀寫功耗與傳統(tǒng)的SRAM比較如下:

(1)對于寫入功耗

傳統(tǒng)的SRAM:

式中:PBL代表主位線上的功耗;PSBL代表局部位線上的功耗;CBL代表局部位線的電容負(fù)載;CSBL代表主位線的電容負(fù)載;CCVBL代表傳統(tǒng)結(jié)構(gòu)位線的電容負(fù)載;VBL代表局部位線的電壓擺幅。通過之前的分析,有(CBL+CSBL)CCVBL,VBLVDD。所以,顯然HBLSA-SRAM的寫入功耗小于傳統(tǒng)的SRAM。

(2)對于讀出功耗

傳統(tǒng)的SRAM:

式中:VCVBL代表讀出傳統(tǒng)結(jié)構(gòu)的位線電壓擺幅。可以認(rèn)為,VCVBL和VBL近似相等,所以HBLSA-SRAM的讀出功耗也小于傳統(tǒng)的SRAM。

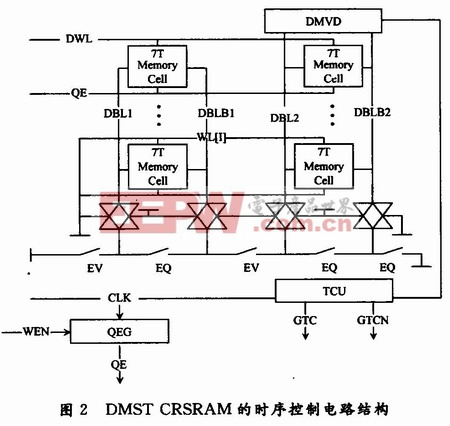

2 基于位線循環(huán)充電SRAM模式的自定時(shí)電路設(shè)計(jì)

將位線循環(huán)充電SRAM的結(jié)構(gòu)與雙模式自定時(shí)電路相結(jié)合,為了進(jìn)一步減小CRSRAM的功耗和優(yōu)化器讀寫延時(shí),提出基于位線循環(huán)充電SRAM的雙模式自定時(shí)電路結(jié)構(gòu)(DMST CRSRAM)。其時(shí)序控制電路如圖2所示。本文引用地址:http://www.104case.com/article/180310.htm

評論