基于位線循環充電SRAM模式的自定時電路設計

引言

近些年來,隨著集成電路制造工藝和制造技術的發展,SRAM存儲芯片在整個SoC芯片面積中所占比例越來越大,而SRAM的功耗也成為整個SoC芯片的主要部分。同時,CPU的工作頻率逐年提高,從1999年的1.2 GHz增長到2010年的3.4 GHz。而且,這一趨勢還在進一步加強。CPU工作頻率的增加對SRAM的工作頻率提出很高的要求。

針對以上,提出位線循環充電(CRSRAM)SRAM結構,它主要是通過降低位線電壓的擺幅來降低功耗。采用雙模式自定時電路(DMST)則主要是根據讀寫周期的不同來產生不同的時序信號,從而提高讀寫速度。基于不同SRAM存儲陣列結構,雖然這種技術能有效地改善SRAM的功耗和速度,但它們卻從來沒有被有效地結合在一起。

本文的主要內容就是設計并仿真基于位線循環充電SRAM結構的雙模式自定時電路(DMST CRSRAM),并將其仿真結果與傳統結構相比較,由此可以看出這兩種結構在速度和功耗方面的優勢。

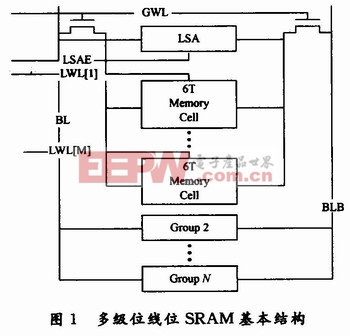

1 多級位線位SRAM結構及工作原理

如圖1所示,多級位線SRAM(HBLSA-SRAM)的主要原理是利用兩級位線和局部靈敏放大器來使主位線寫入周期中的,BL和BLB上的電壓擺幅是一個很小值,而通過局部靈敏放大器將這個電壓放大為VDD到0的大擺幅信號輸入到局部位線上。這樣,位線的電壓擺幅減少,而且VDD到O的大擺幅寫入保證了足夠的寫裕度。

評論