基于Cadence_Allegro的高速PCB設計信號完整性分析與仿真

2.3 對AD數(shù)據(jù)信號的仿真分析

對ADC通道A第0位的SI仿真如圖5所示。本文引用地址:http://www.104case.com/article/178953.htm

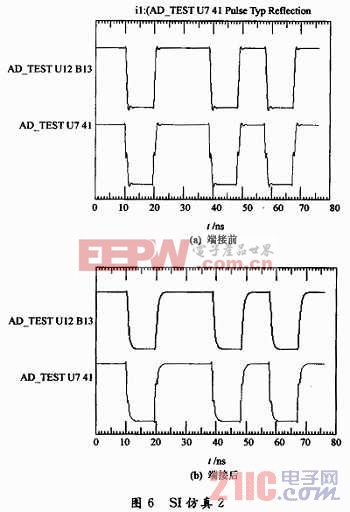

如圖6所示,采用端接電阻后數(shù)據(jù)波形質量明顯提升,端接能有效解決阻抗不匹配所引起的反射問題。

3 結語

Cadence_Allegro軟件中的Specctraquest和Sigxp組件工具,為高速PCB的設計與仿真提供了強有力的支撐,包括仿真模型驗證、拓撲分析、布線前與布線后仿真、約束條件的設置、PCB布局布線等硬件環(huán)節(jié),通過仿真結果可促使設計者較好地把握信號完整性問題,優(yōu)化設計,提高高速PCB設計的一次成功率,較好地應對高速設計所面臨的挑戰(zhàn)。

評論