Delta-Sigma A/D轉換器原理及其PSpice仿真

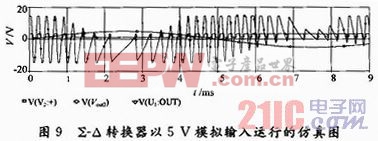

用平均串行比特流的方法可以從該電路獲得并行二進制數輸出。例如,用一個計數電路搜集在一個給定時鐘脈沖中觸發器輸出1的總數(正輸入電壓數輸出0的總數),該計數器的值可以用來表示模擬輸入電壓。圖9是∑-△轉換器以5 V模擬輸入運行的仿真圖。本文引用地址:http://www.104case.com/article/178365.htm

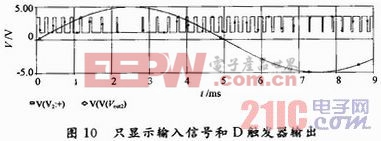

圖中,正弦波是輸入信號,方波是D觸發器輸出的串行比特流,三角波是積分器的輸出波形。圖10只顯示輸入信號和D觸發器輸出。

從圖10中可以清楚地看到輸入信號對輸出脈沖寬度和頻率的調制,輸出是占空比隨模擬輸入電壓大小變化的1,0位流。

3 PSpice仿真對不同電壓幅度的輸入信號積分器參數的調整

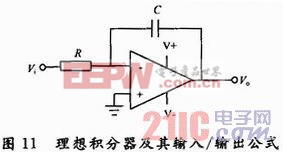

對不同幅度的輸入信號,需要調制積分器的參數,以提高A/D轉換的精度。圖11是理想積分器及其輸入/輸出公式,其中RC是積分器的積分常數。

![]()

對應本文的電路R1、R5和C1決定積分器的時間常數,R1C1是輸入信號的積分常數,R5C1是反饋信號的積分常數。改變電阻或電容值會改變轉換精度。改變C1會同時改變輸入信號和反饋信號的時間常數,當輸入信號的幅值范圍變化時通過改變R1來提高轉換精度要好一些。通過對R1的參數掃描可以看出積分器時間常數對轉換精度的影響。

通過參數掃描分析可知,電阻增加,減小了輸入信號的強度,脈沖直接的間距減小,脈沖之中包含更少的“0”或“1”,說明轉換精度降低。但是R1也不能太小,如果R1太小在對應輸入信號幅值較高處會丟失一些脈沖,也就是丟失了數據。時間常數的選取要根據實際需求中輸入信號波形的幅值范圍進行反復仿真以獲取最佳參數,并用實際電路測試來確定。

4 小信號輸入的仿真例子

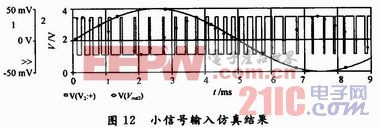

前面在說明∑-△轉換器原理時輸入信號電壓幅值為5 V,實際應用中很多情況下輸入信號是毫伏量級的,下面對幅值為0.05 V(50 mV)的正弦信號進行仿真。用參數仿真的方法確定R1=1.1kΩ。仿真結果如圖12所示。

5 結語

∑-△A/D轉換器具有非常高的分辨率,而且噪聲很低,因為它采用了過采樣的技術,因此對于前端的抗混疊濾波器的要求也大大降低,一般一個簡單的RC低通濾波器就足夠了。這類ADC的線性度也非常好,目前已成為實現高精度A/D轉換的主要方式,但是它付出的代價是采樣速率的降低。另外,由于內部濾波器對于模擬信號的突變和通道的切換需要相對長的建立時間,而且輸出的數據與模擬輸入之間有較長的延時,所以這類A/D轉換器適用于那些模擬信號近似于直流或變化很慢的應用,如溫度測量、壓力測量等,近年來在音頻領域也有應用。

比較器相關文章:比較器工作原理

評論