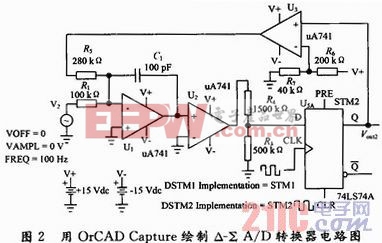

Delta-Sigma A/D轉換器原理及其PSpice仿真

2.1 繪制電路圖

先用OrCAD Capture繪制△-∑A/D轉換器電路圖,如圖2所示。信號源采用FREQ=100 kHz的正弦信號。偏移VOFF=0,幅度先設置為0 V,AMPL=0。本文引用地址:http://www.104case.com/article/178365.htm

為方便起見圖中所有的運算放大器都使用uA741模型,因為這個模型很容易找到,實際項目中根據需要選用合適的運放。D觸發器使用74LS74。在CaptureCIS Lite Edition 9.2和PSpice Lite Version 9.2中沒有74LS系列的元件符號庫74ls.olb也沒有仿真庫74ls.lib,可以從下面的網站下載:

http://power.teipat. gr/download/OrCAD/OrCAD%20Libraries/Library%20for%20Capture/PSPICE/

74LS系列是低功耗肖特基型TTL器件,輸入高電平最小為2.0 V,輸入低電平最大為0.8 V;輸出高電平最小位2.7 V,輸出低電平最大為0.5 V。采用R3和R4分壓將U2的輸出電壓轉換為0~3.75 V電壓,以適應TTL輸入電平。74LS模型只接受正電壓作為電平信號,所以可以不理會比較器U2的負電壓輸出。R6和R7分壓15 V為2.5 V作為參考電壓,將74LS74的TTL輸出電平通過U3轉換為V+/V-的電壓信號。D觸發器的時鐘由DSTM1提供。從74LS74的產品手冊可知,當LCR和PRE端都為高電平時,在時鐘的上升沿,D觸發器將輸入端D的數據送到輸出端Q,并鎖存到下一個時鐘的上升沿。這個高電平由DSTM2提供。圖3是在Stimulus Editor中顯示的STM1和STM2的波形,雙擊波形可以對它進行編輯。

2.2 輸入信號電壓幅度為0 V的情況

從功能上說,△-∑A/D轉換器的轉換結果是一個由觸發器輸出的串行比特流。如果模擬輸入是0 V,積分器將不會有趨向正或負的斜坡,積分器只響應反饋電壓。在這種情況下,觸發器輸出將持續在“高”和“低”之間震蕩輸出,反饋系統前后搜索,試圖維持積分器輸出在0 V。圖4是∑-△轉換器以0 V模擬輸入運行的示意圖,圖中方波是D觸發器輸出,三角波是積分器輸出的。

比較器相關文章:比較器工作原理

評論