Delta-Sigma A/D轉換器原理及其PSpice仿真

摘要:為了深入理解Delta-Sigma A/D轉換器的工作原理,合理地使用這類A/D轉換器產品,或者用FPGA實現自己的Delta-Sigma A/D轉換器設計。采用PSpice仿真軟件進行模擬仿真的方法,對不同幅度的輸入信號進行了一階Delta-Sigma A/D轉換器仿真實驗,獲得了與理論相一致的結果。通過對元件的參數掃描仿真為實際電路設計中元件的選擇提供了實驗依據。仿真實驗過程完整,易于重復,與純數學推導相比,仿真具有直觀的特點。

關鍵詞:Delta-Sigma;A/D轉換器;過采樣;PSpice仿真

0 引言

Delta-Sigma A/D轉換器具有高分辨率、高集成度、成本低和使用方便的特點,近年來,因數字化產品對高分辨率A/D,D/A轉換器需求的激增而得到廣泛地應用。Delta-Sigma A/D轉換器的構想出現已有很多年了,早期因受集成電路制造技術的限制,未在產品中廣泛使用,隨著集成電路制造成本不斷降低,該技術的應用漸多,目前已成為高精度ADC的主流技術。隨著該技術的趨熱,有更多人想了解其工作原理,但目前國內的教材對其涉及還不多,期刊論文多側重數學演繹,文獻中未見有詳盡的仿真實例。

除了制造專用ADC,該技術還易于用FPGA實現,邏輯電路可以完全集成在FPGA內部,只需要很少的外圍元件,就可以用FPGA直接進行混合信號處理。由于FPGA可擴展和可重配置的特性,特別適合產品研發和小規模生產的場合,另外用FPGA在單一芯片上實現多路Sigma-Delta A /D轉換也很容易。

Delta-Sigma有時稱其為Sigma-Delta,或∑-△。

1 Delta-Sigma A/D轉換器原理

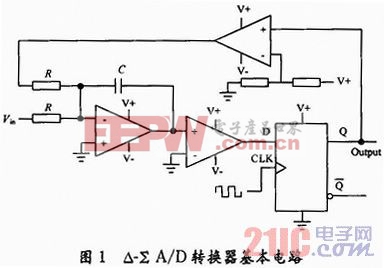

在△-∑A/D轉換器中,模擬輸入電壓信號被連接到一個積分器的輸入端。在輸出端對應輸入大小產生一個電壓變化率,或者斜坡。然后用比較器將該斜坡電壓與地電位(0V)進行比較。比較器的行為就像1位A/D轉換器,根據積分器的輸出是正或負產生1位的輸出(“高”或“低”)。比較器的輸出通過一個以很高頻率時鐘驅動的D觸發器被鎖存,并且反饋到積分器的另一個輸入通道,向0V方向趨勢驅動積分器。基本電路如圖1所示。

在圖1中,最左邊的運放是積分器。積分器饋入的下一個運放是比較器,或1位A/D轉換器。接下來是D觸發器,在每個時鐘脈沖鎖存比較器的輸出,發送“高”或“低”信號到電路頂部的下一個比較器。最后這個比較器用于轉換信號極性,將觸發器的0 V/5 V邏輯電平輸出轉換到V+/V-電壓信號再反饋到積分器。

如果積分器輸出是正,第一次比較器將輸出一個“高”信號給觸發器的D輸入。在下一個時鐘脈沖,“高”信號將從Q線輸出到最后一個比較器的放大器輸入。最上面的那個比較器將看見一個輸入電壓大于+1/2 V的閾值電壓,它向正方向飽和,發送一個滿V+信號到積分器的另一個輸入端。這個V+反饋信號向負方向驅動積分器輸出。如果輸出電壓一直為負,反饋環將發送一個矯正信號(V-)回到積分器的頂部輸入,向正方向驅動它。這就是△-∑行為的概念:第一個比較器感知在積分器輸出和0 V電壓之間的差(△),積分器求模擬輸入信號與最上面比較器輸出的和(∑)。

2 PSpice仿真

通過PSpice仿真模擬實驗,可以更容易和更清楚地理解△-∑A/D轉換器的工作原理。下面采用PSpiee仿真△-∑A/D轉換器。本文使用CaptLire CIS Lite Edition 9.2繪制電路圖,用PSpice Lite Version 9.2進行仿真。

比較器相關文章:比較器工作原理

評論