一種高速低功耗LVDS接收器電路的設(shè)計(jì)

摘要 介紹了LVDS系統(tǒng)鏈路結(jié)構(gòu)及數(shù)據(jù)傳輸原理,分析了LVDS標(biāo)準(zhǔn)對(duì)接收器電路的需求,文中基于65 nm數(shù)字CMOS工藝設(shè)計(jì),實(shí)現(xiàn)了一種高速低功耗LVDS接收器電路。仿真結(jié)果表明,在2.5 V電源電壓工作下,該LVDS接收器具有2 Gbit·s-1的數(shù)據(jù)傳輸速率,平均功耗為3 mW。

關(guān)鍵詞 低壓差分信號(hào)(LVDS);接收器;差分信號(hào);高速

隨著高清多媒體處理器、高性能數(shù)字信號(hào)處理器和網(wǎng)絡(luò)終端技術(shù)的發(fā)展,數(shù)據(jù)傳輸速率的要求越來(lái)越高。集成電路工藝的快速發(fā)展使得芯片內(nèi)部千兆比特每秒數(shù)據(jù)傳輸速率成為可能,然而芯片與芯片之間、不同系統(tǒng)終端之間的傳統(tǒng)接口電路,成為制約整個(gè)系統(tǒng)數(shù)據(jù)傳輸速率提高的障礙。

低電壓擺幅差分信號(hào)(Low Voltage Differential Signal,LVDS)接口,是20世紀(jì)90年代提出的一種高速數(shù)據(jù)傳輸和接口技術(shù),由美國(guó)國(guó)家半導(dǎo)體公司率先提出,并于1996年通過(guò)為IEEE標(biāo)準(zhǔn)。其核心是采用低電壓擺幅高速差分地傳輸數(shù)據(jù),LVDS技術(shù)可以實(shí)現(xiàn)點(diǎn)對(duì)點(diǎn)或一點(diǎn)對(duì)多點(diǎn)的連接,具有低功耗、低誤碼率、低串?dāng)_和低輻射等特點(diǎn)。目前LVDS接口電路廣泛集成在高速ADC、DSP等芯片內(nèi)部解決高速數(shù)據(jù)傳輸?shù)慕涌趩?wèn)題。

1 LVDS系統(tǒng)鏈路原理及接收器電路分析

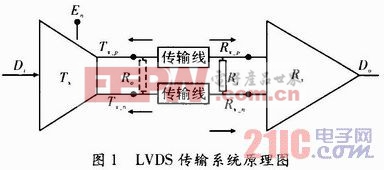

LVDS傳輸系統(tǒng)原理如圖1所示,發(fā)送器將輸入的CMOS電平的數(shù)字信號(hào)轉(zhuǎn)換成差分LVDS信號(hào)進(jìn)行通信傳輸,差分信號(hào)通過(guò)傳輸線到達(dá)接收器電路,接收器電路將差分LVDS信號(hào)轉(zhuǎn)換成CMOS信號(hào)供后續(xù)數(shù)字處理電路處理。在信號(hào)傳輸線的輸入和輸出端,考慮到高頻信號(hào)的反射需要阻抗匹配電阻。在LVDS系統(tǒng)中,信號(hào)差分驅(qū)動(dòng)輸出,在接收端連接一個(gè)100 Ω的電路以匹配傳輸線上單端阻抗50Ω。

由于發(fā)送器和接收器系統(tǒng)間通常距離較遠(yuǎn),互連線電阻會(huì)引入共模電平變化;而且LVDS為全差分傳輸,噪聲通常以共模噪聲的形式耦合到傳輸線上,為提高噪聲容限,IEEE Std.1596.3-1996(LVDS)標(biāo)準(zhǔn)對(duì)接收器輸入共模電平的變化允許1 V。同時(shí),為了消除輸入信號(hào)的不確定性,接收器的輸入要求有約25 mV的遲滯。因此接收器電路一般包括一個(gè)寬共模范圍的前置放大器和遲滯比較器。根據(jù)模擬集成電路設(shè)計(jì)規(guī)則,接收器需要在各種PVT條件下滿足LVDS標(biāo)準(zhǔn)對(duì)接收電壓閾值VTH,IN輸入差分遲滯電壓VHyst和輸入共模電平VCM,IN的規(guī)定如下

|VTH,IN|≤100mV

VHyst≥25mV

0≤VCM,IN≤2.4V

2 接收器電路設(shè)計(jì)

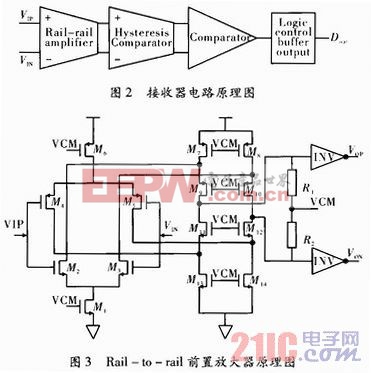

新型低功耗接收器電路原理如圖2所示。該接收器電路有Rail-rail前置放大器、遲滯比較器、差分轉(zhuǎn)單端比較器和邏輯控制及驅(qū)動(dòng)電路組成。其中Rail-rail前置放大器的原理如圖3所示,該前置放大器由Rail-rail輸入差分對(duì)構(gòu)成的折疊式運(yùn)算放大器組成;Rail-rail輸入差分對(duì)保證了寬共模范圍的輸入,折疊式共源共柵輸出階電路保證了增益需求的同時(shí)具有較寬的輸入信號(hào)帶寬,滿足高速信號(hào)傳輸?shù)囊螅惠斎氩罘謱?duì)的微電流源以及負(fù)載電流源偏置由輸出共模電壓提供,既降低了功耗又簡(jiǎn)化了偏置電路。遲滯比較器的原理如圖4所示,該遲滯比較器由偽差分輸入對(duì)和二極管負(fù)載以及負(fù)阻二極管構(gòu)成。差分輸入遲滯電壓由二極管負(fù)載管M18和負(fù)阻二極管M20的尺寸決定。

DIY機(jī)械鍵盤相關(guān)社區(qū):機(jī)械鍵盤DIY

評(píng)論