一種新型的交流電源信號發生器的設計

3 解決的關鍵問題

3.1 防誤計數設計

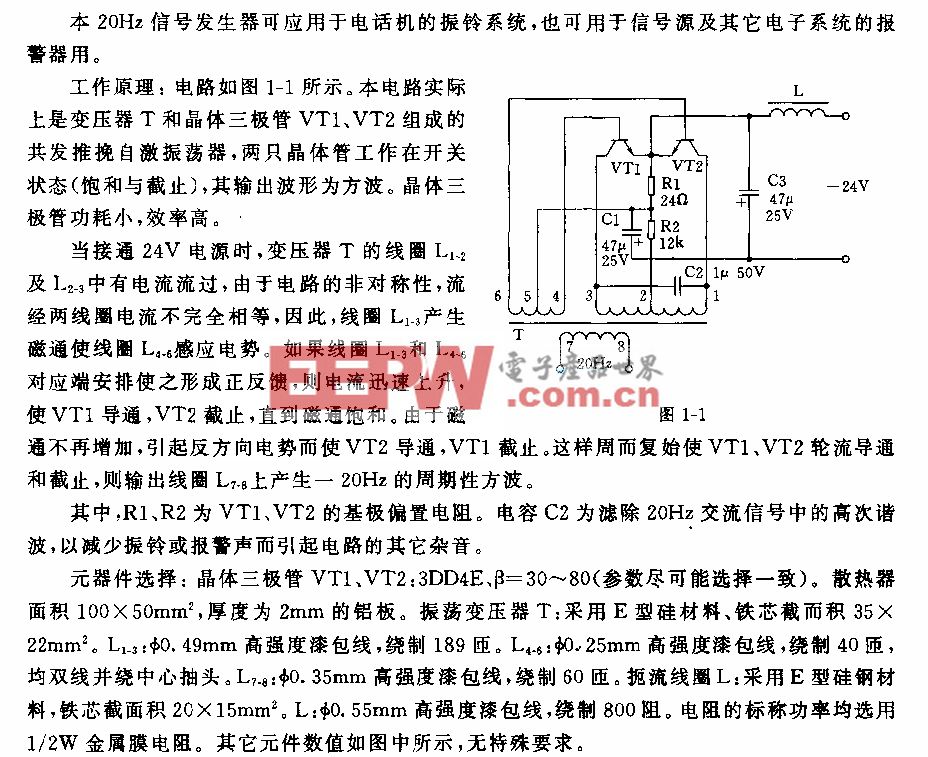

計數器通過檢測時鐘輸入的跳變沿進行計數。初始上電由于電源過沖及時鐘輸入毛刺等原因,會造成計數器的誤計數。為了防止此現象的出現,上電時計數器清零,增強電路的可靠性,電路框圖如圖8所示。本文引用地址:http://www.104case.com/article/175951.htm

,其中時間常數τ=RC。

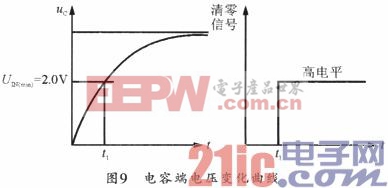

上電后電容端電壓變化曲線如圖9所示。

電容端電壓經整形電路可以得到計數器清零控制信號,圖9中UIH(min)=2.0 V是后端整形電路輸入高電平門限電壓(TTL標準),電壓從0升高到UIH(min)所用的時間為,則UIH(min)=2.0V

![]()

整形后低電平持續時間T1=t1。需要注意的是設計阻容時為滿足時序,要求T1≤T2,T2是晶振的振蕩周期。

3.2 三相信號設計

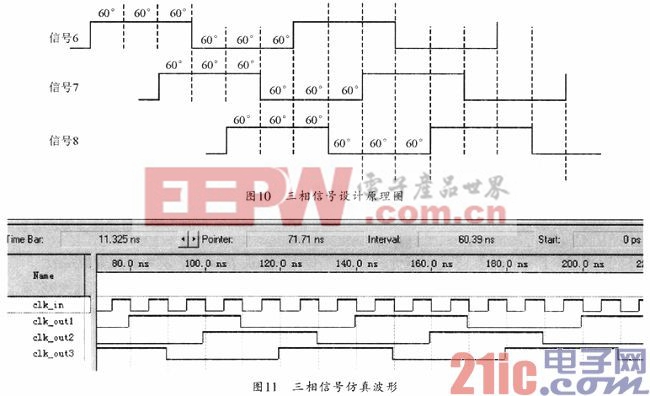

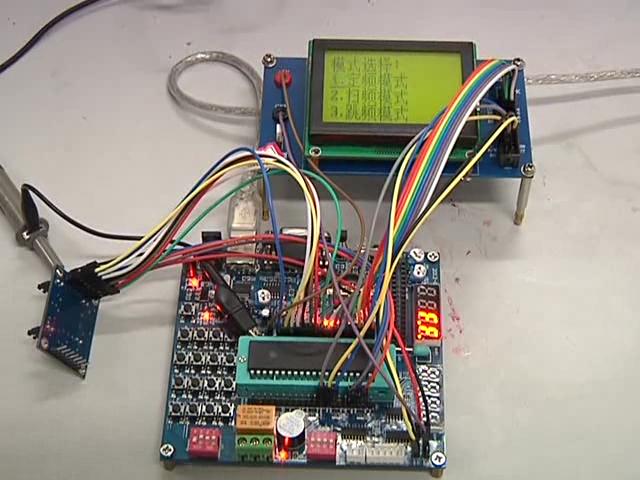

信號1~信號5為晶振頻率基準16.384 MHz的整數倍,分頻占空比調整信號頻點理論誤差為0,信號6~信號8要求1kHz相差120°輸出。1個周期T為360°細分6段每段為60°,以60°為間隔三相信號輸出對應不同的邏輯電平,即可得到120°相差的信號,電路實現原理圖如圖10所示。

從圖10可以看出將品振基準頻率16.384MHz進行2371次分頻看得到6 kHz作為移相輸入頻率,移相間隔為1 kHz,在1個計數周期T即6 kHz內,信號6~信號8對應邏輯電平輸出見表1。

電路仿真波形如圖11所示,實驗波形見圖7。

3.3 高精度分頻器設計

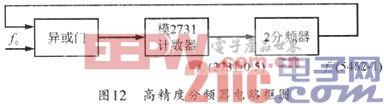

電路信號輸出精度要求小于10-3,信號1~信號5均為基準頻率的整數倍分頻精度均有滿足要求,信號6~信號8采用整數倍2731次分頻精度可達1.2x10-4,雖也滿足指標要求,但在高溫和低溫情況下隨著基準頻率的溫漂精度出現了臨界情況。為了有效解決1 kHz頻率精度的問題,需要設計高精度的分頻器,設計了2730.5次分頻,電路結構框圖如圖12所示。

從圖12可看出將基準頻率分頻2730.5次得到6.000366 kHz經過相移電路可以得到三相信號頻率為1.000061 kHz,頻率精度為6.1× 10-5。由上可以看出,設計半整數分頻器比整數分頻器得到的信號頻率精度高出一個數量級,實驗證明在高低溫情況下,電特性完全滿足指標要求。

4 結束語

本電路采用一片CPLD (16×16 mm)實現了2730.5分頻器、32分頻器、三個16位計數器、一個6分頻器、一個邏輯分配器的功能,只占用了該芯片69%的邏輯資源和36%的輸入/輸出口(I/O口)。

本文詳細闡述了交流電源信號發生器的工作原理及其在系統中的功能,介紹了常規的信號發生裝置的設計方法,并比較了其優劣勢。采用可編程邏輯器件設計了交流電源信號發生器,這種新型方法具有信號輸出精度高、抗干擾能力強、體積小、設計修改方便、成本較低等優勢,為其他相似電路的設計提供了參考。

評論