電能計(jì)量芯片Sigma-Delta ADC降采樣濾波器設(shè)計(jì)(一)

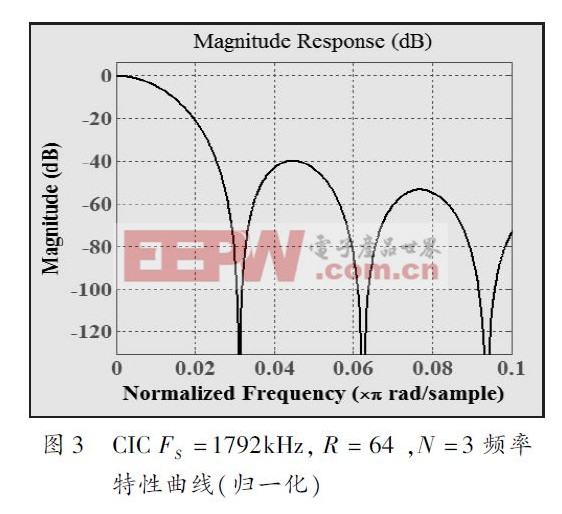

由于Σ-△為二階調(diào)制器,因此,三階CIC 濾波器即可達(dá)得很好的抽取效果.假定延遲因子為1,則內(nèi)部寄存器的長度L = (N*(log2R ) + 1) 為19bit.采樣定點(diǎn)算法,內(nèi)部寄存器量化為Sfix34. En15,輸出為Sfix24. En23.由CIC 濾波器的結(jié)構(gòu)以及幅值響應(yīng)公式可知,當(dāng)R 足夠大時,信號通過CIC 濾波器時,幅值將會被放大[RM]N 倍,此設(shè)計(jì)中為643 ,因此,需將CIC輸出右移18 位,消除增益對信號的影響.圖3 為通過MATLAB 仿真得到FS =1792kHz, R = 64,N = 3 的歸一化(0 - 0. 1)幅頻特性曲線.

2 半帶濾波器的設(shè)計(jì)

第二級的抽取濾波器用于衰減經(jīng)過第一級梳狀濾波器后混疊在基帶內(nèi)的信號分量和量化噪聲分量.由于電能計(jì)量對信號有嚴(yán)格的線性相位要求,所以必須采用FIR 型濾波器.半帶濾波器是一種特殊的線性相位濾波器,它的偶數(shù)系數(shù)都為零(中間位系數(shù)為0. 5),因此其實(shí)現(xiàn)濾波的運(yùn)算量與同樣長度的其它線性相位濾波器相比減少一半,這將進(jìn)一步減小芯片面積.降低電路的功耗.

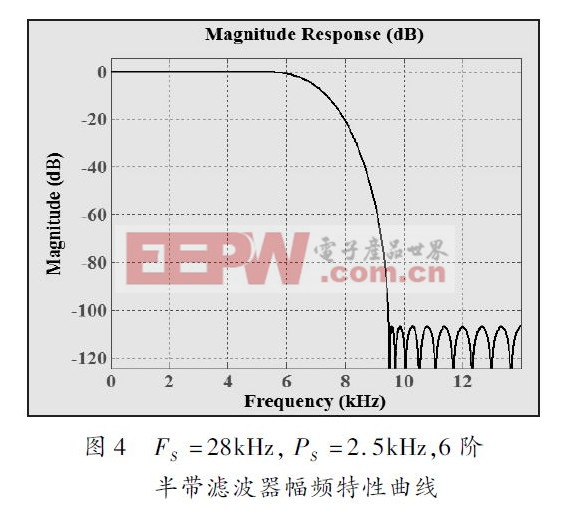

綜合考慮芯片面積以及系統(tǒng)的頻率響應(yīng),HBF 設(shè)定為6 階.考慮到正弦信號的高次諧波以及CIC 補(bǔ)償濾波器的通帶頻率,HBF 的通帶頻率設(shè)定為2. 5kHz.

由于HBF 的系數(shù)值很少,量化精度不夠?qū)⒂绊懴到y(tǒng)的傳輸特性,仿真到的系數(shù)采用Sfix48. En47 Bit,內(nèi)部乘法器采用Sfix56. En55 Bit 可滿足系統(tǒng)要求,而考慮到補(bǔ)碼定點(diǎn)數(shù)加法有可能產(chǎn)生溢出,所以加法器量化為Sfix56. En54 Bit.圖4 為通過MATLAB 仿真得到的HBF 幅頻特性曲線.

HBF 的運(yùn)算包括乘法以及加法,而乘法運(yùn)算的功耗最大.傳統(tǒng)的乘法運(yùn)算采用移位相加的原理,相加次數(shù)等于乘數(shù)中1 的個數(shù),因此減少乘數(shù)中1 的個數(shù)即可降低乘法電路的功耗.CSD 編碼正好滿足這一要求,經(jīng)過CSD 編碼后,將乘法系數(shù)中1 的個數(shù)降到最低,從而減少加法(或減法)的次數(shù).CSD 編碼含三重值{1,0,-1},編碼原則是從最低有效位開始,用100…0(-1) 來取代所有大于2 的1 序列.例如上述HBF中乘法系數(shù)b (3)= 0. 28847028573567002,量化后b(3)= 48′h24EC98258D1E(Sfix48_En47),則對應(yīng)的CSD 編碼b (3)= 0+00+0+000-0-00+0+0-00000+0+0-0-00+0-0+00+000-0(“+”表示1,“-”表示負(fù)1).

x(n)*b(3) = – (x(n) 1) + x(n) 5 + x(n) 8 – (x(n) 10) + x(n) 12 + … + x(n) 40 + x(n) 《44,因此,經(jīng)CSD 編碼后, b (3)的乘法運(yùn)算變成只有10 次加法和7 次減法運(yùn)算,與傳統(tǒng)的移位相加相比,減少了運(yùn)算的次數(shù),從而降低了HBF 的功耗.

評論