基于高分辨率CMOS傳感器圖像采集系統的實現

硬件設計主要體現在CPLD的邏輯上面。本系統采用ALTERA公司的CPLD芯片EPM240作為系統的邏輯控制器件,有80個I/O引腳和240個邏輯單元,資源足夠滿足各種方式的采集設計的需要。

DSP采用TI公司的TMS320C6711DSK板,TMS320C6711DSK有以下特點:

(1)板上留有2個80腳的接口,方便系統擴展;

(2)EMIF接口有兩種時鐘模式可以選擇,時鐘頻率分別為150MHz和100MHz;

(3)100MHz的16MB同步動態存儲器(SDRAM);

(4)直接提供1.8V和3.3V直流電源;

(5)JTAG仿真器,可支持并口或外接XDS510支持;

(6)1個并行接口,主機可通過該并口訪問開發板上的存儲器;

(7)150MHz主頻,可執行900 MFLOPS浮點操作;

(8)128KB的可編程Flash存儲器;

(9)16位語音CODEC電路。

2.2 CPLD內部的邏輯

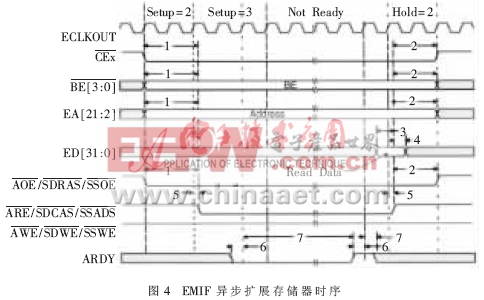

TMS320C6711的EMIF口連接異步存儲器的時序如圖4所示。

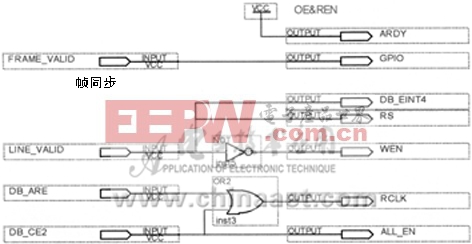

從時序圖可以看出, 在 的上升沿便讀取一次數據,所以用這個引腳來作為讀取FIFO的時鐘最合適。如果用ECLKOUT讀取,需要在CPLD中設計計數器,很不方便,也不靈活。圖5為CPLD內部邏輯圖。

的上升沿便讀取一次數據,所以用這個引腳來作為讀取FIFO的時鐘最合適。如果用ECLKOUT讀取,需要在CPLD中設計計數器,很不方便,也不靈活。圖5為CPLD內部邏輯圖。

圖5 邏輯連接圖

3 軟件設計

3.1 圖像傳感器的配置

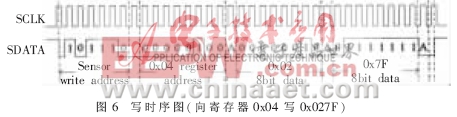

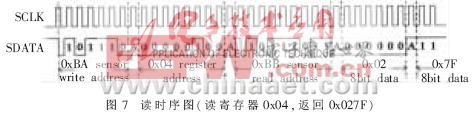

SCLK和SDATA兩條線構成了該串行總線,SCLK為串行時鐘,SDATA為串行數據。兩條線通過1.5kΩ的電阻上拉到3.3V。在實際應用中,通過上拉1.3kΩ電阻,用TMS320VC6711(外擴一片EPM240實現)模擬總線時序,完全可以達到要求。其操作方法幾乎和IIC總線一樣,在速度和位數上稍微有一點差別,限于篇幅不再贅述。圖6為寫時序圖,圖7為讀時序圖。

芯片內部集成了模擬處理電路(10bit A/D轉換器,放大器)、時鐘控制電路(反相,相位調節)、圖像大小調節、原點定位、白平衡調節、曝光調節、幀速率調節等眾多功能電路,所有這些控制都通過一個串行總線口進行操作(SCLK和SDATA)。數據輸出則為10bit并行口,數據同步時鐘PIXCLK,行同步LINE_VALID和幀同步信號FRAME_VALID。

在本系統設計中,由于在綠色通道增益最低的情況下采集到的圖像還是偏綠,所以對紅色和藍色通道的增益調大了少許。

評論