基于高分辨率CMOS傳感器圖像采集系統(tǒng)的實現(xiàn)

隨著CMOS技術(shù)的發(fā)展,原來CMOS圖像傳感器比CCD噪聲大的特點得到大大改善,并且以其成本低、功耗低、單一工作電壓、集成AD轉(zhuǎn)換器、數(shù)字形式數(shù)據(jù)輸出、圖像大小可編程控制等優(yōu)點,在攝像頭、微型數(shù)碼照相機、掃描儀、手機、可視電話、視頻會議等眾多領(lǐng)域應(yīng)用。但要將CMOS的圖像采集到DSP芯片中的硬件設(shè)計成本較高,實現(xiàn)難度較大。現(xiàn)階段,比較多的方案是采用帶視頻控制器的DSP芯片,如TI6000系列中帶有3個VPO接口的TMS320DM642和ADI公司帶PPI接口的Blackfin處理器。很多低價通用的DSP如TI55x系列和67x系列的DSP,與CMOS圖像傳感器都沒有直接接口,需要設(shè)計硬件電路。本文便是針對這種低價通用的DSP,提出的一種低成本的采集方案。

1 系統(tǒng)設(shè)計

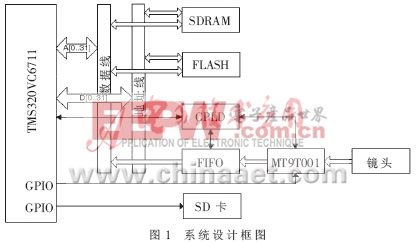

由于大部分DSP都有與SDRAM、Flash、SRAM、FIFO等存儲器接口的EMIF接口,而沒有直接與CMOS/CCD固體圖像傳感器接口的控制器。所以采用CPLD作為圖像傳感器到FIFO以及FIFO到DSP的一個時序協(xié)調(diào)控制器。同時由于圖像傳感器的像素時鐘PIXCLK很高,最高可以達到48MHz,固體圖像傳感器的圖像數(shù)據(jù)量大,而FIFO的容量有限,一般都是幾K、幾十K字節(jié),對于高像素的圖像來說,F(xiàn)IFO只能充當線緩沖的作用,要作為幀緩沖,除非系統(tǒng)對速度要求很高,否則成本太高。由于采集到DSP中的圖像數(shù)據(jù)量很大,靠寫文件的方式來驗證采集的數(shù)據(jù)非常慢,所以本系統(tǒng)采用GPIO設(shè)計了一個SD卡的控制器,通過寫B(tài)MP文件,對采集的圖像進行驗證。系統(tǒng)設(shè)計框圖如圖1所示。

本系統(tǒng)設(shè)計的關(guān)鍵在于DSP采用何種方式去讀取FIFO中的圖像數(shù)據(jù)。很多方案中都是啟動EDMA讀取FIFO中的圖像數(shù)據(jù),當FIFO半滿時中斷DSP啟動EDMA讀取數(shù)據(jù),這樣對FIFO讀時鐘的頻率要求很高,需要讀時鐘為寫時鐘的2倍。但這種方案存在問題,即FIFO時鐘的選擇問題。EMIF口的 在EDMA啟動的過程中都是一些不穩(wěn)定不規(guī)則的負脈沖信號,難以選擇作為FIFO的讀時鐘。這種采用EDMA的方案在TMS320DM642中可行,因為TMS320DM642能與FIFO無縫連接。

在EDMA啟動的過程中都是一些不穩(wěn)定不規(guī)則的負脈沖信號,難以選擇作為FIFO的讀時鐘。這種采用EDMA的方案在TMS320DM642中可行,因為TMS320DM642能與FIFO無縫連接。

2 硬件設(shè)計

2.1 硬件電路圖

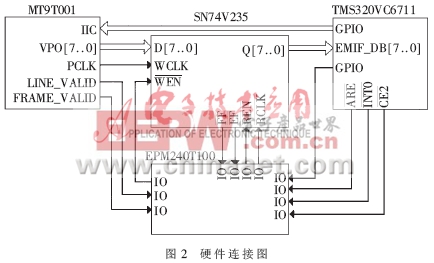

本系統(tǒng)硬件連接如圖2所示,所采用的圖像傳感器型號是MT9T001,它是一款主要針對數(shù)碼相機領(lǐng)域的CMOS圖像傳感器。與其他的CMOS圖像傳感器相比,MT9T001有以下明顯的特點:

(1)像素大小可以通過IIC接口改變相應(yīng)寄存器進行硬件裁剪。

(2)高的幀速,輸出為QXGA分辨率(2 048×1 536)時,可以達到12f/s,而輸出為VGA分辨率(320×240)時,有93f/s。

(3)高性能的低照度成像性能。

(4)具有AF對焦窗口的圖像輸出格式,如圖3所示,(2 048×512)時,可以達到30f/s。

評論