利用SoC平臺設計并驗證MPEG-4/JPEG編解碼IP

本文引用地址:http://www.104case.com/article/167069.htm

鋸齒狀掃描(Zigzag Scan):經過量化之后,每個 8 x 8 的小方塊里面除了左上角區域以外其它部份幾乎都會變為0。為了把連續 0 的個數予以編碼,對每個8 x 8 的小方塊做鋸齒狀掃描,使得二維變成一維。鋸齒狀掃描單元支持所有MPEG-4及JPEG鋸齒狀掃描方法。鋸齒狀掃描單元產生的結果在編碼的狀態送到VLC單元。反鋸齒狀掃描單元產生的結果在解碼的狀態送到AC/DC預測單元。

可變長編解碼器(Variable Length Coding/Dec

oding, VLC/VLD):當資經過運動估計(ME),DCT,量化及AC/DC預測后,VLC 經由適當的編碼成流,再透過網傳輸流交由使用者端的解碼器譯碼成MPEG4 的影像。可變長編碼器(VLC)是一種和霍夫曼編碼法相同的功能,常出現的值用較短的碼值,少出現的用長的碼值達到較好的壓縮比,因此,會先建一個碼簿配合查表動作。另外,為怕有的值在碼簿中搜查到,所以提出固定長編碼法除這些額外的值。我們在進查表前先進資掃描的動作,其中掃描可分為三種方式,分別為Horizontal Scan、Vertical Scan 及ZigZag Scan。VLC/VLD單元支持MPEG-4 固定VLC和JPEG客戶定義霍夫曼編碼方法。VLC單元產生的結果在編碼的狀態是最后的壓縮比特流。VLD單元產生的結果在解碼的狀態送到鋸齒狀掃描單元。

運動補償(Motion Compensation, MC):在做運動估計的同時已經做了一些假設,假設畫面中的物體不會放大或縮小、變型或旋轉、突然出現或消失,但在真實的世界里這些假設不恒成立。如果只做運動估計,重建畫面與原始畫面會產生誤差,而且隨著畫面數目增加而增加。為了彌補運動估計的不足,必須設計運動補償單元。在編碼的狀態,運動補償單元將原始區塊減去內插產生的區塊,剩余的區塊送到DCT單元。在解碼的狀態,運動補償單元將IDCT單元產生的區塊加上內插區塊產生重建的區塊。

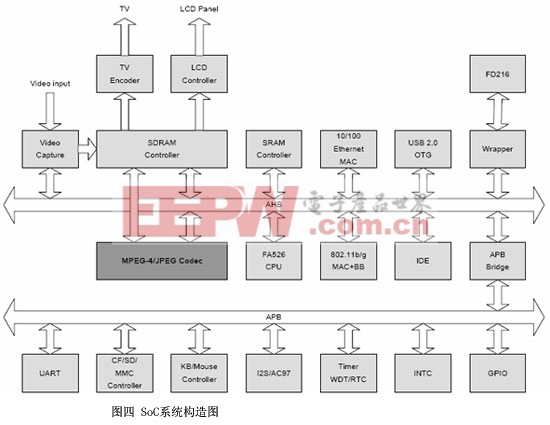

圖四所示為一SoC系統構造圖,包括了FA526 CPU,MPEG4/JPEG編解碼器,視頻輸入輸出接口和MPEG4/JPEG編解碼器所需的系統內存控制器。視頻捕獲(video capture) 接口執行傳遞視頻數據到系統內存的任務。

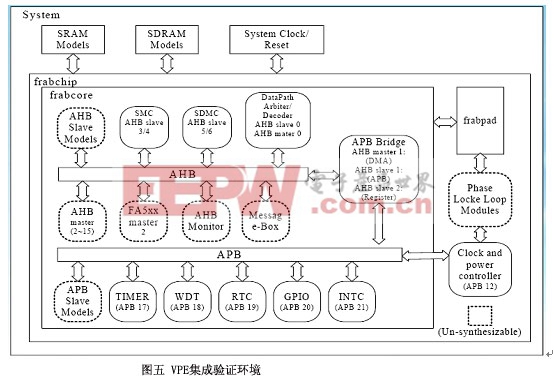

接著使用智原科技的虛擬平臺環境(VPE)驗證MPEG4/JPEG模塊的時序。如圖五所示,智原科技的VPE系統是一個通用的基于高級微控制器總線架構(AMBA)的SoC集成驗證環境。設計者可以使用VPE與EDA仿真器驗證IP的功能以及SoC芯片的完整性。它集成了

智原科技CPU仿真模型

AMBA總線器件仿真模型(master/ slave / arbiter / decoder … )

智原科技 starcells仿真模型(sdmc, gpio, smc …. )

其它相關器件仿真模型(sdram/ rom/ I/O model )

設計者可以根據需要添加自己的設計,例如掛在AHB上的MPEG4編解碼器。每一個功能模塊都可以在VPE中獨立仿真。智原科技可在VPE上提供了AMBA的各個功能模塊的仿真模型,設計者可以很方便的搭建起一個基于AMBA的SoC系統并進行測試。其VPE的仿真模型包括下列:

行為級模型(Behavioral Model)

-AHB 主器件(Master)

-AHB 從器件(Slave)

-AHB 監視器(Monitor)

-APB 從器件(Slave)

RTL 級模型

-仲裁器(Arbiter)

-解碼器(Decoder)

-有直接存儲器存取(DMA)通道的AHB-to-APB橋接器

-沒有直接存儲器存取(DMA)通道的AHB-to-APB橋接器

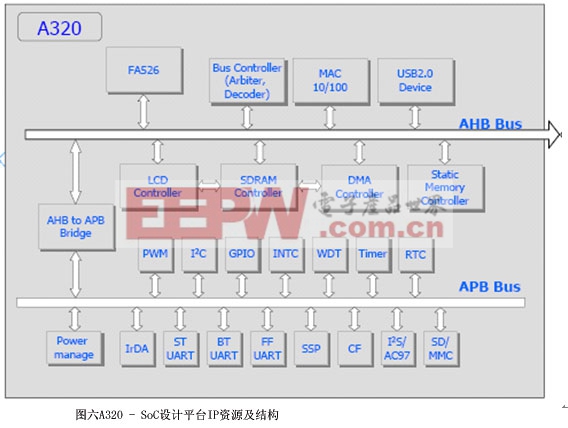

完成了功能仿真后,我們利用如圖六所示A320的SoC設計平臺做FPGA硬件仿真,A320集成了完成設計所需的IP。用FPGA實現的邏輯模塊通過AHB/APB總線連接器與A320設計平臺連接,可以很方便地完成功能驗證,調試等一系列動作。因為A320芯片上的IP均為硅驗證,在驗證設計的同時也保證了從設計到芯片的一致性。

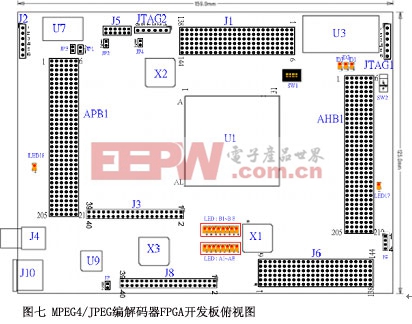

我們設計了一款能與A320進行驗證的FPGA開發板,如下圖七所示。MPEG4/JPEG編解碼器開發板包括Xilinx Virtex-II XC2V4000 BF957, 視頻捕獲和A320接口。他提供了板上FPGA (XC2V4000 BF957),SAA7113 視頻捕獲芯片,CMOS傳感器模塊,16個LED用以顯示調試的信息,2個擴展總線和一個AHB連接器連接A320開發板。我們也制作文檔說明Pin腳的定義,方便使用者理解設計原理。

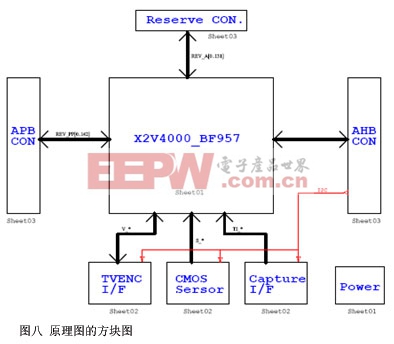

我們也提供原理圖給使用者,如下圖八所示,使用者可完全理解訊號流的走向。

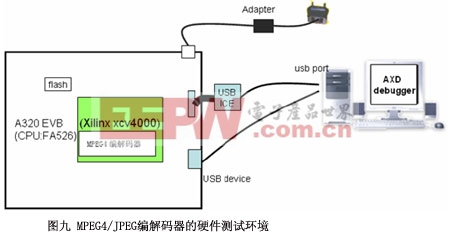

我們的測試環境很方便,如下圖九所示,利用ARM的軟件開發環境,

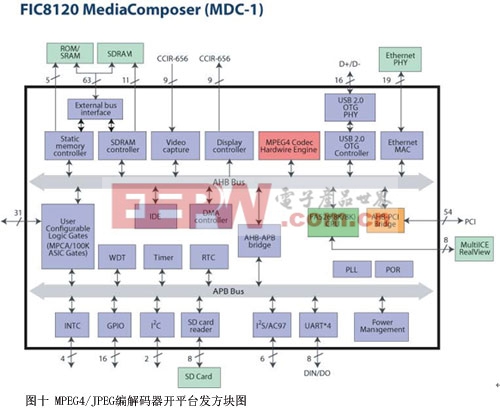

完成FPGA驗證的MPEG4/JPEG編解碼器可與A320平臺上的IP結合,再加上其它需要的IP,如AHB-PCI橋等共同流片,就是另一個平臺(如下圖十)或是一個針對音/視頻的成品。平臺化能因為大量已預先驗證過的架構而加快設計時間。平臺化也是利用IP復用方法設計SoC。SoC設計開發平臺實際上是一個綜合的開發系統。其中核心芯片集成了常用的IP,為開發提供了最基礎的支持。開發測試板提供了硬件的開發環境,VPE提供了軟件仿真的環境。使用VPE平臺,SoC系統的開發變得簡潔、高效。好的驗證及開發平臺使帶有MPEG4/JPEG編解碼器的SoC能快速的完成設計,驗證及流片,智原科技的A320平臺就是一個好的SoC驗證及開發平臺。

評論