基于NiosII的IP Camera傳輸系統實現

1 引言

本文引用地址:http://www.104case.com/article/166901.htm隨著網絡技術的發展,人們對監控功能要求越來越高,網絡攝像頭以其特有的優勢改變了傳統監控手段,為遠程實時監控提供了出色的解決方案。人們只需打開網頁或視頻瀏覽器就可實時查看需要監控場所的安全情況。

2 系統的硬件設計

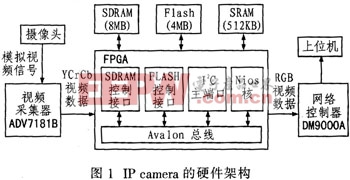

IP Camera的硬件架構如圖1所示,這是筆者參與開發的一種基于Altera公司NiosII嵌入式軟核CPU的網絡視頻傳輸設計方案,實現了以太網內視頻數據傳輸。FPGA采用的是Altera公司的Cy-cloneII系列的EP2C35F672C6器件。IP camera主要是由視頻采集、Cyclone FPGA及系統存儲和網絡傳輸等3部分組成。由于Cyclone FPGA及系統存儲的電路設計具有一定的通用性,所以這里僅介紹視頻采集和網絡傳輸的電路設計。

2.1視頻采集模塊設計

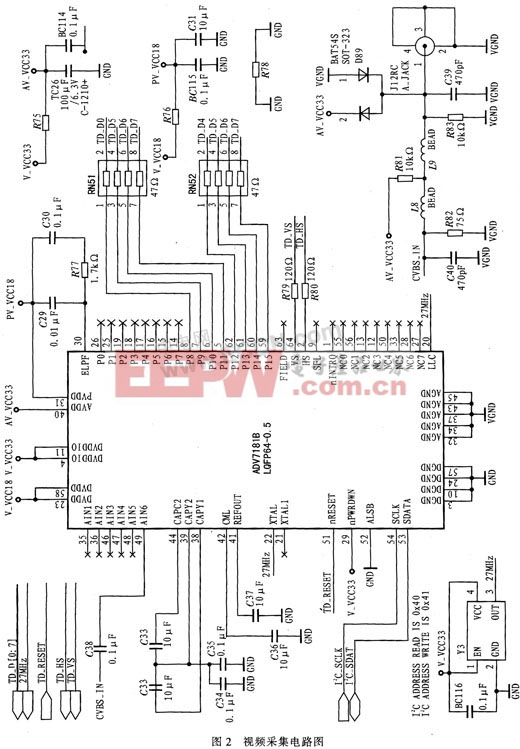

本系統設計的視頻采集器件采用ADV7181B。ADV7181B是一款集成的視頻解碼器,通過配置可以接收CVBS復合視頻、S-Video及YPrPb分量多種模擬信號,ADV7181B的數字輸出是16位或8位、并與CCIR656標準兼容的YCrCb4:2:2視頻數據,還包括垂直同步VS、水平同步HS及場同步信號。

本系統設計選用ADV7181B的AIN6作為CVBS復合視頻信號的輸入,ADV7181B的輸出數據采用8位的數據寬度。ADV7181B的27 MHz時鐘由FPGA提供,FPGA通過I2C總線讀/寫ADV7181B的寄存器控制ADV7181B,ADV7181B的I2C總線讀地址為0x40,寫地址為0x41。ADV7181B的8位YCrCb4:2:2視頻輸出數據及其他輸出信號直接連接至FPGA。視頻采集電路模塊電路圖如圖2所示。

tcp/ip相關文章:tcp/ip是什么

評論