PAL一體化攝像機設計

C27,R27,VD6,C23構成自舉升壓電路,把CXDl267發(fā)出的VSUB信號轉換為CCD可接受的電壓幅值,即SUB信號,它是電子快門控制信 號,通過控制傳感器像素表面的電荷積累時間操縱快門。當電子快門關閉時,對于PAL攝像機,CCD電荷累積時間為1/50 s。電子快門則以311步的基本單位覆蓋,其范圍1/50~1/10 000 s。當電子快門速度增加時,在每個視頻場允許的時間內,聚焦在CCD上的光減少,結果將降低

攝像機的靈敏度。

AFE周邊電路設計如圖4所示。

CXA2096N采用3.3 V供電,其主要作用是對模擬電信號進行采樣、保持、放大,封裝是24引腳SSOP(Plastic)。CCD送出的模擬信號CCD-OUT,經2SKl875放大后傳輸給 CXA2096N,經CXA2096N采樣、保持、放大后得到DRVOUT信號傳輸給DSP。CXA2096N是信號進行模數(shù)轉換前的最后一 個環(huán)節(jié),其重要性不言而喻,同樣地,CXA2096N也是在DSP時鐘發(fā)生器的時序驅動信號下完成其一系列工作的。其中最重要的3個信號分別是CCDLEVEL、OFFSET和AGCCONT。

CCDLEVEL是CXA2096N的輸出信號,這個信號直接反映了CCD采集到信號的電平大小、變化程度和范圍。CCD正常情況下采集到的黑電平信號約2.7 V。

OFFSET是CXA2096N的輸出信號,變化范圍1.5~3 V,這個信號反映的是一個偏移量,DSP可以通過它改變CXA2096N的采樣偏置電壓,這一改變直接反應在視頻顯示處理板中,體現(xiàn)到最終的圖像顯示效果 上。OFFSET越大,圖像整體向明亮的區(qū)域變化,反之,則往黑暗的區(qū)域變化。因為OFFSET信號使得圖像整體偏移變化,用一個形象的比喻,它是一個 “加”的關系,即圖像數(shù)據(jù)整體增加了一個偏置電平。AGCCONT也是CXA2096N的輸出信號,變化范圍1.5~3 V,這個信號反映的是一個增益量,所有一體化攝像機都有一個來自CCD的信號放大到可以使用水準的視頻放大器,其放大量即增益,等效于較高的靈敏度,可使 其在微光下靈敏,然而在亮光照的環(huán)境中放大器將過載,使視頻信號畸變。為此,需利用一體化攝像機的自動增益控制(AGC)電路去探測視頻信號的電平,適時 地開關AGC,從而使攝像機能夠在較大的光照范圍內工作,即動態(tài)范圍,在低照度時自動增加攝像機的靈敏度,從而提高圖像信號的強度來獲得清晰的圖像。外部 單片機或DSP可以通過改變CXA2096N的放大增益系數(shù),直接反應在視頻顯示處理板中,體現(xiàn)到最終的圖像顯示效果上。AGCCONT越大,圖像整體向 明亮的區(qū)域變化,反之,則往黑暗的區(qū)域變化。因為AGCCONT信號使得圖像整體偏移變化,即圖像數(shù)據(jù)整體“乘”增益系數(shù)。

CXA2096N的采樣需要一個基準電壓,否則采樣的數(shù)據(jù)會有偏差,這對將來的視頻數(shù)據(jù)處理影響非常大的。采樣校準電壓VRT和VRB一定要保證準確,VRT為2.35 V,是采樣上限:VRB為1.35 V,是采樣下限。同時VRT和VRB輸出給A/D轉換器,作為其量化的參考電平。

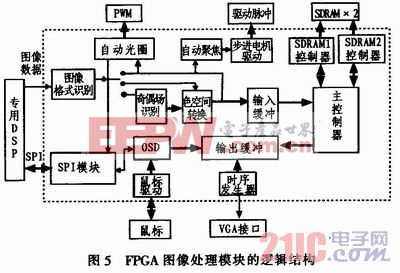

1.2 FPGA圖像處理模塊

該模塊的邏輯結構如圖5所示。該模塊基于FPGA設計,實現(xiàn)自動聚焦、自動光圈控制、幀率提升、OSD以及SPI通信功能。FPGA采用XILI-NX公司的XC3S250E。內部功能采用自頂向下的層次式設計方法,并用VHDL硬件描述語言實現(xiàn),最終由ISE 6.0綜合生成位流,固化在外部的存儲器中。本文引用地址:http://www.104case.com/article/166316.htm

FPGA將接收的YUV(4:2:2)格式的信號進行格式識別和轉換,然后在SDRAM中把連續(xù)2場圖像緩沖為一幀圖像,下一幀圖像緩沖在另一片 SDRAM中,形成了連續(xù)切換視頻雙緩沖結構。當其中一片SDRAM輸入圖像時,另一片在VGA顯示控制器的控制下通過輸出FIFO以SVGA@60Hz 的點速率輸出圖像,具體過程如下:

該模塊首先對輸入信號進行奇偶場識別,奇場掃描的第一行有374個像素,偶場掃描的第一行有748個像素,通過對一場的第一行數(shù)據(jù)計數(shù)判斷,可知當前場為 奇場或偶場,然后從下一個奇場開始接收數(shù)據(jù)。這樣確保了相鄰兩場為一幀完整的圖像。此模塊為深度748、寬度16 bit的異步FIFO(先進先出),寫地址計數(shù)器為0到748的循環(huán)計數(shù)器,當其計數(shù)到300或700時,給主控制器發(fā)送讀信號,主控制器隨后產生 FIFO的讀使能信號,使讀使能信號在連續(xù)的374個讀時鐘周期內一直有效,即可連續(xù)讀出374個數(shù)據(jù)。本設計讀時鐘頻率大于寫時鐘頻率,不會產生數(shù)據(jù)寫 滿溢出的現(xiàn)象。

主控制器通過對輸入緩沖的讀請求信號和輸出緩沖的寫請求信號處理,實現(xiàn)對2個SDRAM的讀、寫操作切換。該模塊首先完成對SDRAM的初始 化,SDRAM被設置成連續(xù)的全頁進發(fā)模式。然后SDRAM進入正常工作狀態(tài),準備接收讀、寫命令。當SDRAM在空閑狀態(tài)下,為保持其數(shù)據(jù)不丟失,必須 對其定時刷新,一般要求64ms內刷新4096次,但是當SDRAM在進行讀、寫進發(fā)時,自動刷新命令會打斷讀、寫,從而造成數(shù)據(jù)丟失。該設計在64 ms內對SDRAM至少進行4 096次讀、寫操作,所以可以不必對其刷新。當SDRAM讀、寫到374時,發(fā)出預充命令來停止進發(fā),同時關閉當前行,為下一次讀、寫作好準備。 SDRAM被設置成進發(fā)模式,進發(fā)長度為374。

首先時序發(fā)生器利用40 MHz的主時鐘產生符合VESA標準的行、場同步信號,同時在行、場參考信號都有效,且39行計數(shù)器788、19場計數(shù)器604時產生輸出緩沖的讀使能信號。輸出模塊為深度748、寬度16 bit的異步FIFO。寫時鐘和讀時鐘同為40 MHz的主時鐘,當讀使能有效時,啟動讀計數(shù)器從O到799循環(huán)計數(shù)。該設計每隔10個數(shù)據(jù)將前一個數(shù)據(jù)重復讀出,直到輸出800個數(shù)據(jù)。當讀計數(shù)器計到100或500時,該模塊向主控制器模塊發(fā)寫請求命令。在行、場消隱期間,讀使能信號無效,所以不會產生讀空現(xiàn)象。

經過PWl226視頻顯示模塊進一步濾波,消除行場間閃爍效應,提高畫質,并可平滑放大到l 024x768的分辨率,最終輸出SVGA或XGA的標準的VGA視頻接口信號。

同時FPGA還可以通過內部的SPI模塊實現(xiàn)對DSP和CXD4103的寄存器設置,使其正常工作。

1.3 自動聚焦

首先,F(xiàn)PGA通過對圖像亮度信號Y的處理來實現(xiàn)自動聚焦功能。選擇常用的灰度差分法作為聚焦評價函數(shù),選取中心像素過去的4個像素(左側、左上側、右側、右上側4個像素)計算差分值。

由于聚焦評價函數(shù)需要用中心像素所在行及上一行臨近的4個像素,所以需要在FPGA內部使用2個雙口RAM做相鄰兩行數(shù)據(jù)緩存區(qū),每個雙口RAM容量為 800x8 bit。讀寫選擇模塊將一幀圖像的第l行數(shù)據(jù)寫入RAMl,將第2行數(shù)據(jù)寫入RAM2。在寫入RAM2一個時鐘周期后,開始讀出RAMl和RAM2中的數(shù) 據(jù),送到聚焦評價函數(shù)算法實現(xiàn)模塊,以RAM2中的圖像像素為中心像素計算亮度差值絕對值和,當?shù)?行圖像數(shù)據(jù)到來時再次寫入RAMl,同樣在寫入 RAMl一個時鐘周期后,讀出RAMl和RAM2中的數(shù)據(jù)并送到聚焦評價函數(shù)算法實現(xiàn)模塊,同樣以RAMl中的像素為中心計算亮度差值絕對值和,如此循 環(huán),得到一場的亮度差值絕對值總和。

評論