基于NAND FLASH的大容量視頻存儲系統(tǒng)的設(shè)計(jì)

FPGA作為DSP的異步外設(shè)連接到DSP的系統(tǒng)總線上,DSP通過存儲器DMA的方式向FPGA發(fā)送數(shù)據(jù)和讀取FPGA內(nèi)部RAM中的數(shù)據(jù)。考慮到FPGA自身I/O引腳數(shù)量的限制和引腳驅(qū)動(dòng)能力,本系統(tǒng)采用兩片F(xiàn)PGA來驅(qū)動(dòng)100片FLASH,FLASH陣列分為25組,每組4片FLASH,共用一套數(shù)據(jù)/地址總線和控制總線,各片F(xiàn)LASH通過片選信號來選中。

DSP的PPI接口接收到的視頻數(shù)據(jù)是經(jīng)過MPEG-4格式壓縮過的,其最大bit流速率為4 Mb/s。PPI的總線時(shí)鐘頻率最大可達(dá)133 MHz,也就是數(shù)據(jù)傳輸速率最大可達(dá)133 M×16 b/s,所以對于4 Mb/s的視頻數(shù)據(jù)完全可以滿足要求。視頻數(shù)據(jù)到達(dá)存儲板后,由FPGA負(fù)責(zé)寫入存儲器,存儲芯片K9WBG08U1M的寫入速率為5MB/s,每路視頻數(shù)據(jù)率為4Mb/s=0.5MB/s,故存儲芯片K9WBG08U1M也可以達(dá)到存儲速率的要求。

2.3 FLASH的驅(qū)動(dòng)設(shè)計(jì)

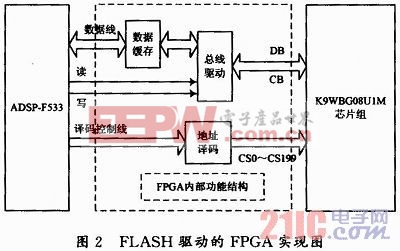

本系統(tǒng)采用FPGA給FLASH提供總線驅(qū)動(dòng)和譯碼邏輯,以其中一片F(xiàn)PGA為例,其具體實(shí)現(xiàn)圖如圖2所示。本文引用地址:http://www.104case.com/article/165555.htm

在FPGA內(nèi)部構(gòu)建兩個(gè)雙口RAM,一個(gè)用于存儲操作,一個(gè)用于下載操作。當(dāng)進(jìn)行存儲操作時(shí),F(xiàn)PGA首先接收DSP發(fā)送的數(shù)據(jù)(包含地址信息)存儲在雙口RAM中,此過程采用MDMA的方式。數(shù)據(jù)接收完成后,DSP給FPGA發(fā)送啟動(dòng)信號,此時(shí)FPGA開始產(chǎn)生FLASH控制時(shí)序?qū)⒋鎯υ陔p口RAM中的數(shù)據(jù)寫入FLASH中,同時(shí)根據(jù)地址信息譯碼產(chǎn)生相應(yīng)的片選信號來選中某一片F(xiàn)LASH芯片。在編程過程中,只要保證下一次MDMA結(jié)束前當(dāng)前頁編程已經(jīng)結(jié)束,就可以產(chǎn)生一個(gè)脈沖通知DSP準(zhǔn)備下一頁寫入操作,這樣可以讓MDMA與編程同時(shí)進(jìn)行,從而提高寫入速率;同理,在進(jìn)行下載操作時(shí),先將FLASH中的數(shù)據(jù)緩存到雙口RAM中,然后通知DSP進(jìn)行MDAM操作即可。圖3給出了存儲操作的功能仿真波形。從圖中可以看出完全滿足FLASH的寫入時(shí)序,經(jīng)驗(yàn)證,此模塊實(shí)現(xiàn)的存儲效果非常好。

評論