主存儲器部件的組成與設計

1、主存儲器概述

本文引用地址:http://www.104case.com/article/165074.htm(1)主存儲器的兩個重要技術指標

◎讀寫速度:常常用存儲周期來度量,存儲周期是連續啟動兩次獨立的存儲器操作(如讀操作)所必需的時間間隔。

◎存儲容量:通常用構成存儲器的字節數或字數來計量。

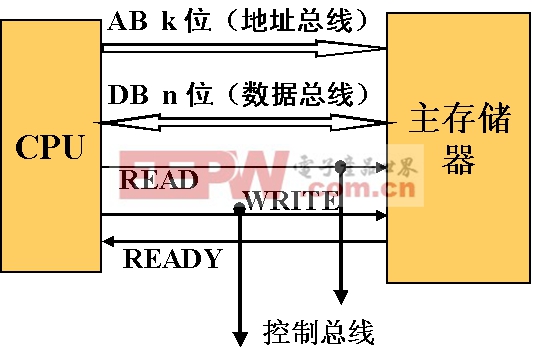

(2)主存儲器與CPU及外圍設備的連接

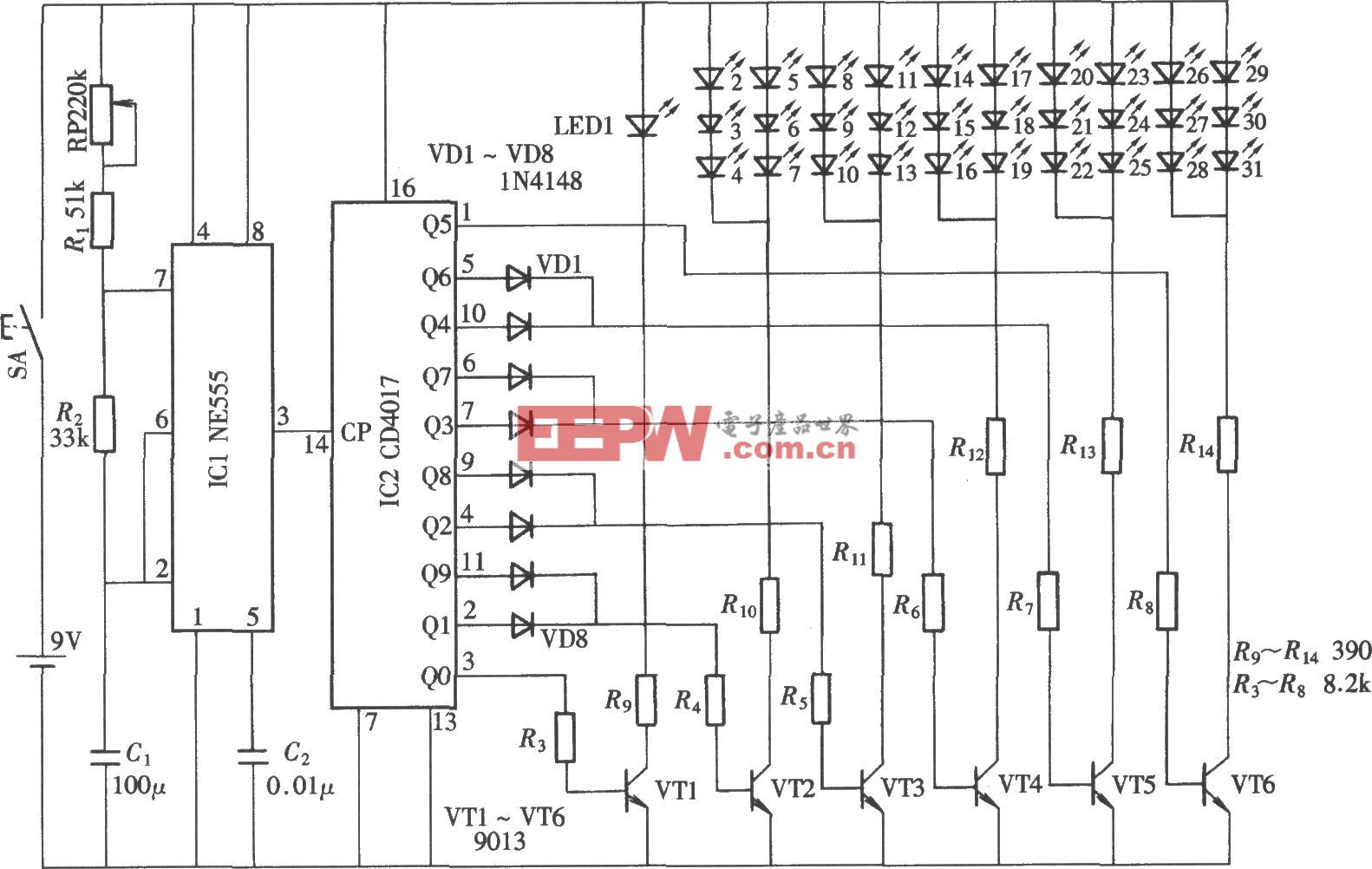

是通過地址總線、數據總線、控制總線進行連接,見下圖

主存儲器與CPU的連接

◎地址總線用于選擇主存儲器的一個存儲單元,若地址總線的位數k,則最大可尋址空間為2k。如k=20,可訪問1MB的存儲單元。

◎數據總線用于在計算機各功能部件之間傳送數據。

◎控制總線用于指明總線的工作周期和本次輸入/輸出完成的時刻。

(3)主存儲器分類

◎按信息保存的長短分:ROM與RAM

◎按生產工藝分:靜態存儲器與動態存儲器

靜態存儲器(SRAM):讀寫速度快,生產成本高,多用于容量較小的高速緩沖存儲器。

動態存儲器(DRAM):讀寫速度較慢,集成度高,生產成本低,多用于容量較大的主存儲器。

靜態存儲器與動態存儲器主要性能比較如下表:

靜態和動態存儲器芯片特性比較

SRAM DRAM

存儲信息 觸發器 電容

破壞性讀出 非 是

需要刷新 不要 需要

送行列地址 同時送 分兩次送

運行速度 快 慢

集成度 低 高

發熱量 大 小

存儲成本 高 低

動態存儲器的定期刷新:在不進行讀寫操作時,DRAM 存儲器的各單元處于斷電狀態,由于漏電的存在,保存在電容CS 上的電荷會慢慢地漏掉,為此必須定時予以補充,稱為刷新操作。

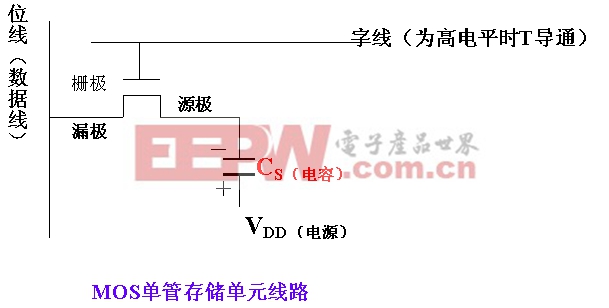

2、動態存儲器的記憶原理和讀寫過程

(1)動態存儲器的組成:由單個MOS管來存儲一位二進制信息。信息存儲在MOS管的源極的寄生電容CS中。

◎寫數據時:字線為高電平,T導通。

寫“1”時,位線(數據線)為低電平, VDD(電源)將向電容充電

寫“0時,位線(數據線)為高電平, 若電容存儲了電荷,則將會使電容完成放電,就表示存儲了“0”。

◎讀數據時:先使位線(數據線)變為高電平,當字線高電平到來時T導通,若電容原存儲有電荷( 是“1” ),則電容就要放電,就會使數據線電位由高變低;若電容沒有存儲電荷( 是“0” ),則數據線電位不會變化。檢測數據線上電位的變化就可以區分讀出的數據是1還是0。

注意

①讀操作使電容原存儲的電荷丟失,因此是破壞性讀出。為保持原記憶內容,必須在讀操作后立刻跟隨一次寫入操作,稱為預充電延遲。

②向動態存儲器的存儲單元提供地址,是先送行地址再送列地址。原因就是對動態存儲器必須定時刷新(如2ms),刷新不是按字處理,而是每次刷新一行,即為連接在同一行上所有存儲單元的電容補充一次能量。

③在動態存儲器的位線上讀出信號很小,必須接讀出放大器,通常用觸發器線路實現。

④存儲器芯片內部的行地址和列地址鎖存器分先后接受行、列地址。

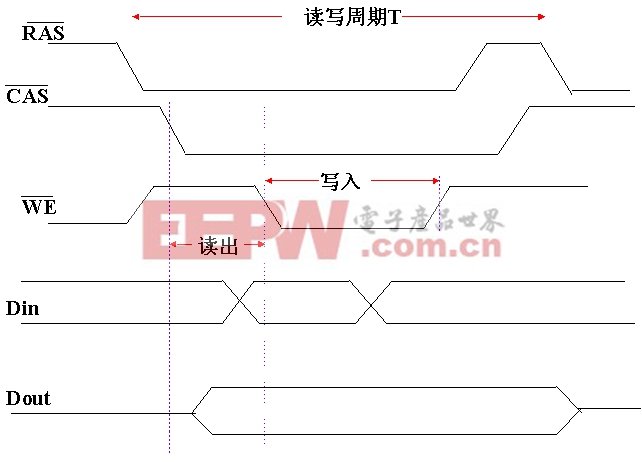

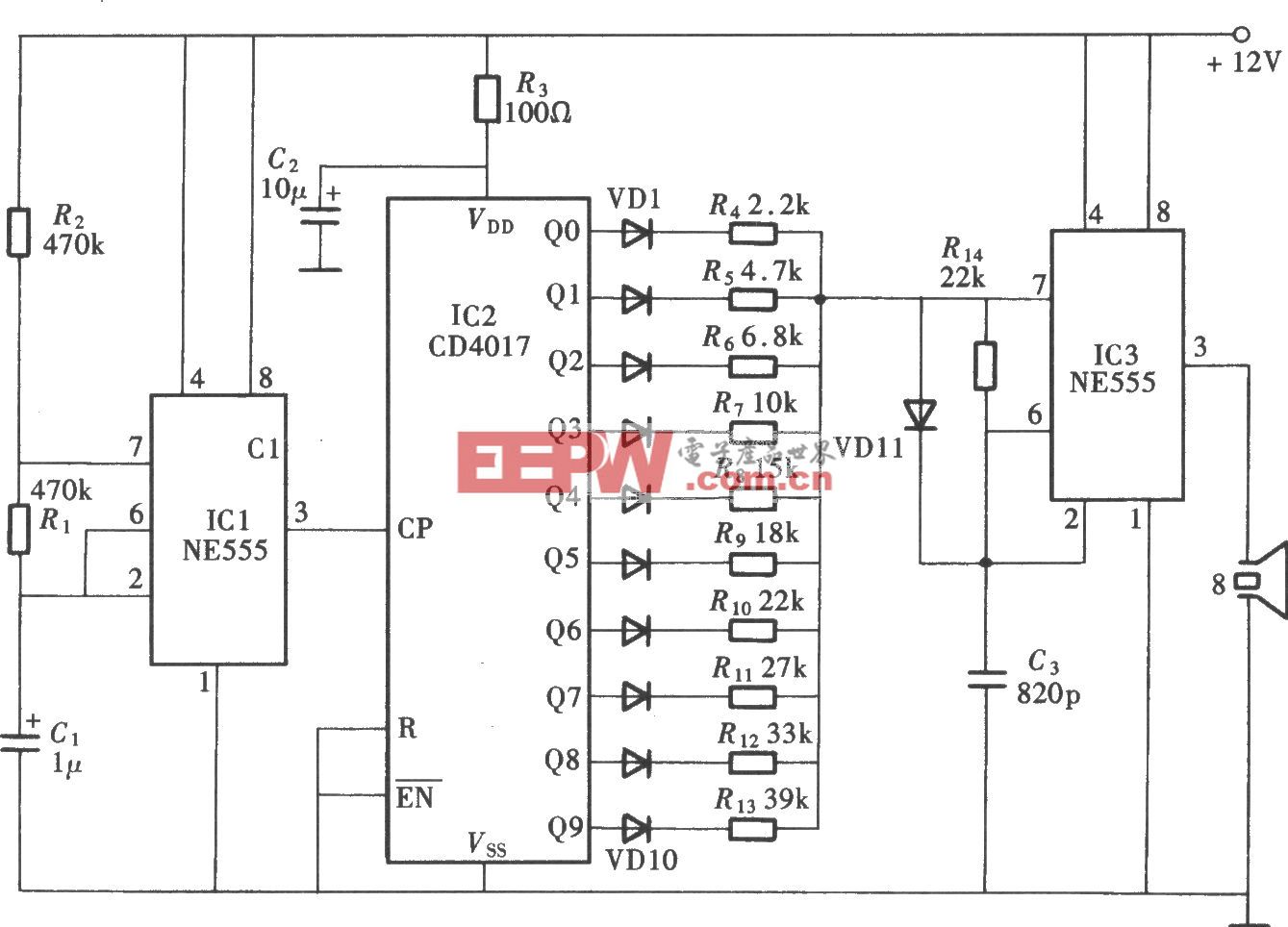

⑤RAS、CAS、WE、Din、Dout時序關系如下圖:

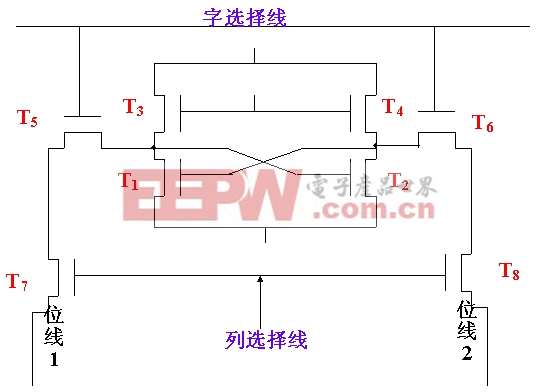

(1)靜態存儲器的存儲原理和芯片內部結構(P207)

◎地址總線:記為AB15~AB0,統一由地址寄存器AR驅動,地址寄存器AR只接收ALU輸出的信息。

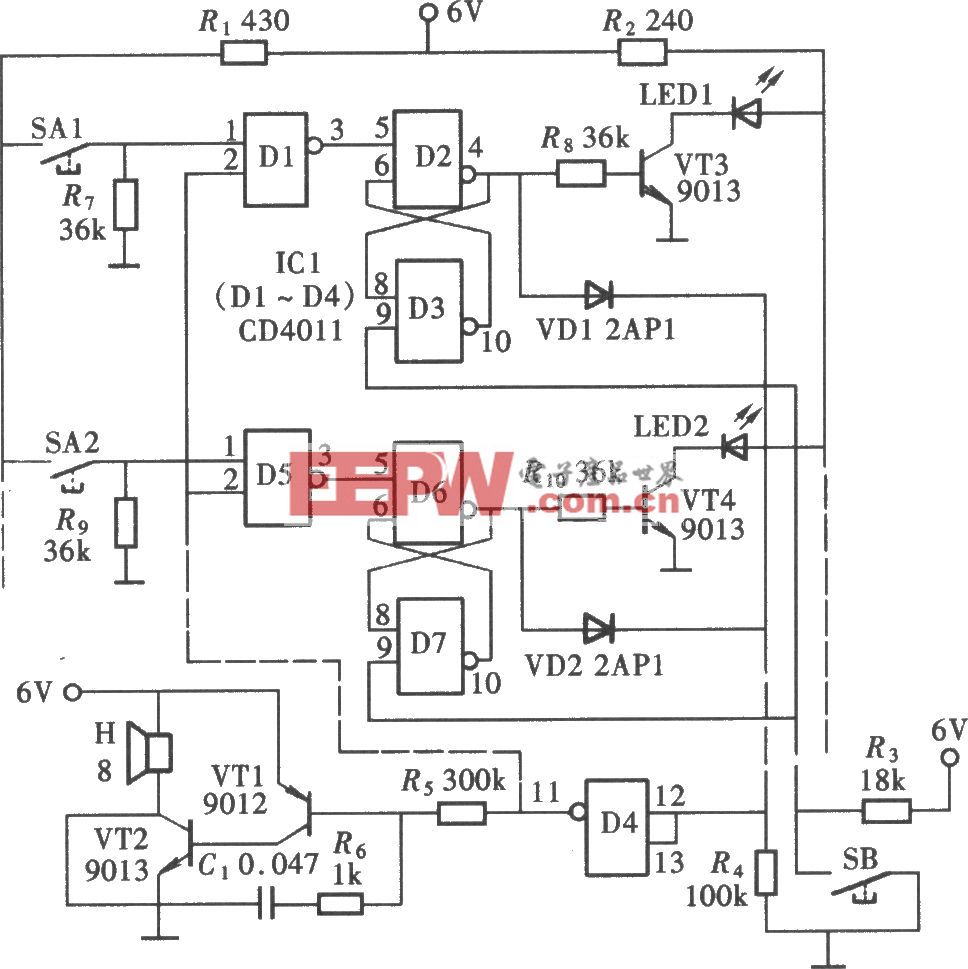

◎控制總線:控制總線的信號由譯碼器74LS139給出,功能是指出總線周期的類型:

※內存寫周期 用MMW信號標記

※內存讀周期 用MMR信號標記

※外設(接口)寫周期 用IOW信號標記

※外設(接口)讀周期 用IOR信號標記

※內存在工作 用MMREQ信號標記

※外設在工作 用IOREQ信號標記

※寫控存周期 用SWA信號標記

◎數據總線:分為內部數據總線IB與外部數據總線DB兩部分。主要完成計算機各功能部件之間的數據傳送。

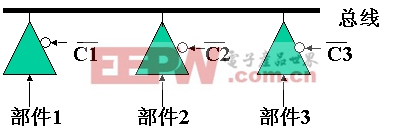

設計總線的核心技術是要保證在任何時刻只能把一組數據發送到總線上,卻允許一個和多個部件同時接受總線上的信息。所用的電路通常為三態門電路。

◎系統時鐘及時序:教學機晶振1.8432MHz,3分頻后用614.4KHz的時鐘作為系統主時鐘,使CPU、內存、IO同步運行。

CPU內部的有些寄存器用時鐘結束時的上升沿完成接受數據,而通用寄存器是用低電平接收的。內存或I/O讀寫操作時,每個總線周期由兩個時鐘組成,第一個時鐘,稱為地址時間,用于傳送地址;第二個時鐘,稱為數據時間,用于讀寫數據

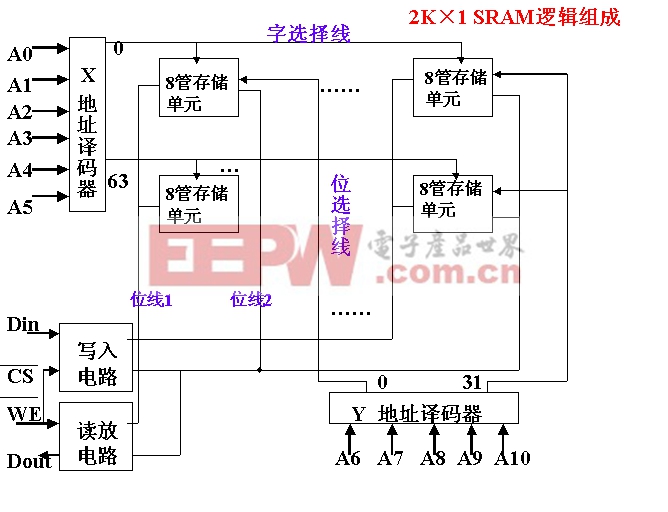

◎靜態存儲器的字位擴展:

教學計算機的內存儲器用靜態存儲器芯片實現,由2K字的ROM區和2K字RAM區組成。內存字長16位,按字尋址。

ROM由74LS2716只讀存儲器ROM(每片2048個存儲單元,每單元為8位二進制位)兩片完成字長的擴展。地址分配在:0~2047

存儲器相關文章:存儲器原理

評論