NiosII的I2C控制IP及其在成像系統中的應用

摘要:詳細介紹一種I2C控制IP的工作原理及其可編程寄存器,給出該IP在CMOS數字成像中的應用實例。該實例基于可編程片上系統(SOPC)技術設計,在NioslI IDE中通過編寫程序來實現系統功能,并通過QuartusII軟件自帶的SignaITapII進行驗證。結果表明,在CMOS成像領域選用該IP核,系統能充分利用SOPC技術的優勢,具有擴展性好、控制靈活、開發周期短等特點。

關鍵詞:SOPC;I2C控制IP;CMOS

1 IP的硬件結構及寄存器

1.1 IP硬件結構

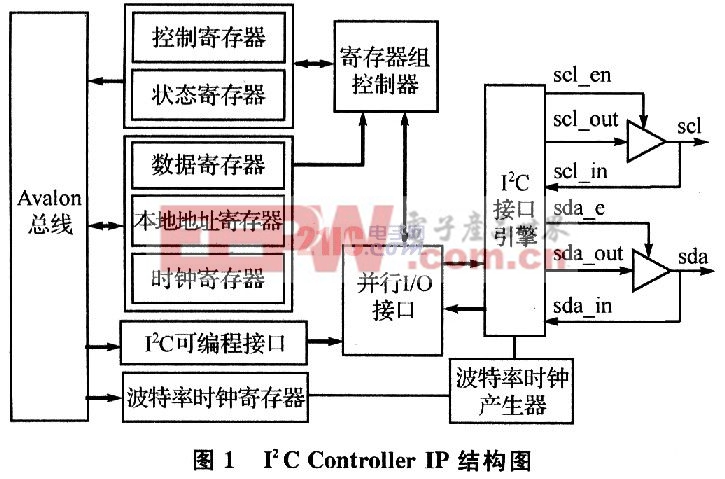

IP內部結構如圖1所示。主要由波特率時鐘寄存器、寄存器組控制器、并行I/O接口、I2C可編程接口、I2C接口引擎5個模塊組成。波特率時鐘產生器用來產生I2C IP工作的基本時鐘頻率;寄存器組控制器用來對寄存器進行設置,設置數據通過并行I/O接口傳送到該模塊中;并行I/0接口模塊用來處理可編程接口模塊傳送過來的命令;I2C可編程接口模塊用來設置IP各個寄存器的地址;I2C接口引擎模塊執行I2C總線上數據的傳輸。

1.2 寄存器結構

I2C控制IP主要由6個寄存器構成,如表1所列。通過對寄存器的讀寫可以方便地控制I2C總線數據的傳輸,從而實現NioslI處理器與設備之間的通信。數據寄存器用來存放I2C總線上要傳送的數據;波特率產生模塊,波特率時鐘寄存器和時鐘寄存器共同決定I2C總線上SCL的頻率。SCL的計算公式為 。其中System_clk是系統時鐘;Value是時鐘寄存器的值;divider是波特率時鐘寄存器的值所對應的分頻數(寄存器的值與分頻數相差為1,如寄存器設置為O,則分頻數為1;寄存器設置為1,則分頻數值為2)。本地地址寄存器、控制寄存器、狀態寄存器的詳細介紹略――編者注。

。其中System_clk是系統時鐘;Value是時鐘寄存器的值;divider是波特率時鐘寄存器的值所對應的分頻數(寄存器的值與分頻數相差為1,如寄存器設置為O,則分頻數為1;寄存器設置為1,則分頻數值為2)。本地地址寄存器、控制寄存器、狀態寄存器的詳細介紹略――編者注。

tcp/ip相關文章:tcp/ip是什么

評論