PSoC在光纖陀螺脈沖輸出采集中的應用

3.2 脈沖采集部分

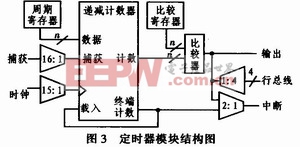

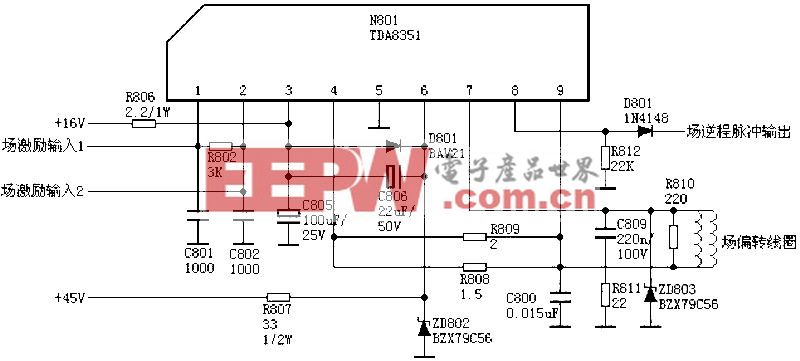

脈沖采集模塊由定時器模塊和計數器模塊組成。PSoC芯片嵌入了強大的定時器功能模塊。它擁有8位、16位、24位和32位可編程遞減定時器。通過對定時器模塊編程,用戶可實現多種工作方式的定時器功能。PSoC的定時器模塊由1個周期寄存器、1個同步遞減計數器和1個捕獲比較寄存器組成,結構如圖3所示,每個寄存器大小都是1個字節。當定時器不工作時,向周期寄存器(Period Register)寫入一個周期值。當定時器工作時,周期值會被自動從周期寄存器中載入到遞減計數器(Down Counter)中,隨后,計數器將會執行遞減計數操作直到0。在下一個時鐘上升沿,周期值將會被重新載入,緊接著繼續計數。遞減計數器模塊主要的功能是輸出信號,它可以被配置成全時鐘循環或者半時鐘循環。定時器具有定時、比較和捕獲比較3種功能。本系統中運用其定時功能。原理如下:將系統的數字時鐘或其他輸入信號作為Clock,通過設置Period值即可獲得相應的定時間隔,定時間隔T=(Period+1)/fClock。當遞減計數器值減為0時,定時器時間到,此時Terminal Counter Out將輸出一個高電平脈沖,若設置了中斷,則將產生定時器中斷。本文引用地址:http://www.104case.com/article/162307.htm

定時器的核心是一個遞減計數的計數器,計數器功能模塊和定時器功能模塊具有相同的結構,都包含1個周期寄存器、1個同步遞減計數器和1個捕獲比較寄存器。兩者的功能模塊主要有如下的區別:

1)計數器的數據輸入是一個計數器的使能位而不是一個捕獲輸入,計數器不能用作異步捕獲,當計數器被使能工作時,數據寄存器不能執行讀操作;

2)比較器輸出作為計數器的主輸出,而計數器終止輸出是作為輔助輸出;

3)計數終止輸出只能是全周期輸出。

本系統中運用計數器的計數功能,其原理是:將光纖陀螺儀脈沖輸出信號作為Clock輸入,預先設定一個Period數值,通過讀取減數計數器DR0數值的變化獲得輸入信號的計數值,計數值C=Period-DR0。

3. 3 顯示器件的選擇

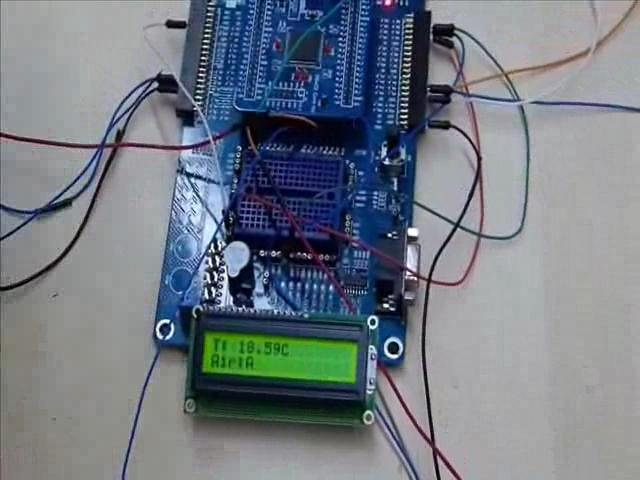

PSoC集成開發環境(IDE)PSoC Designer5.O中有LCD、LED、LED7SEG等顯示器件。由于LCD功耗低、壽命長、價格低、接口控制方便、使用靈活等諸多優點,本系統選用LCD顯示器件。通常液晶顯示器LCD可分為兩大類,一類是點陣型,另一類是字符型。點陣型液晶通常面積較大,可以顯示圖形;而字符型液晶顯示模塊專用于顯示字母、數字和一些簡單圖形,面積相對較小,簡單易控制且成本較低。本系統只需顯示一定時間里的脈沖數,故選用了字符型液晶顯示器1602,它可實現兩行16個字符的顯示。

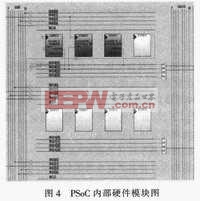

3.4 PSoC內部硬件搭建

在集成開發環境(IDE)PSoC Designer5.0的器件編輯器中,可實現硬件模塊的搭建。本系統只用到了PSoC芯片內部的1個8位定時器、1個16位計數器和1塊LCD用戶模塊。

8位定時器產生1 ms的方波信號,接在16位定時器的使能端,用于控制定時器對光纖陀螺脈沖信號計數,最終的采集結果在液晶顯示器LCD上顯示。PSoC內部硬件搭建如圖4所示。

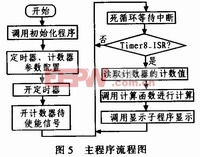

4 軟件設計

系統首先用8位定時器Timer8通過中斷方式產生準確時間,而后調用計數子程序對光纖陀螺脈沖輸出進行計數,最后調用顯示子程序將采樣結果在LCD上顯示出來。其軟件流程如下圖5所示。

需要注意的是,在定時器最終計數結束后的下一個系統時鐘周期,定時器會自動重新加載計數初值。所以要在此之前讀取計數器的計數值。此操作可以通過定時器的中斷程序來實現。

5 測試結果

將應用層代碼下載到PSoC程序下載軟件環境PSoCProgrammer3.06中。進行仿真。本系統選用南京盛普儀器科技有限公司生產的SP1641D型函數信號發生器來模擬光纖陀螺的脈沖輸出信號,測試周期為1 s,測試數據如表1所示。

由表1可看出,本測試系統能夠精確測量頻率范圍在0.1Hz~1MHz之間的光纖陀螺脈沖輸出,并且誤差小于萬分之一,滿足了實際的測試需求。

6 結束語

本設計以PSoC芯片CY29666-24PVXI為核心,完成了光纖陀螺脈沖輸出的高精度采集。測試范圍能夠達到0.1Hz~1 MHz,誤差小于萬分之一。該設計電路簡單、集成度高、性能穩定、抗干擾能力強、價格低廉、且可靠性高,充分體現了PSoC芯片的優點,在對光纖陀螺進行測試,提高光纖陀螺精度方面,有較大的價值。

干涉儀相關文章:干涉儀原理

評論