基于FPGA的攝像機傳感器接口實現

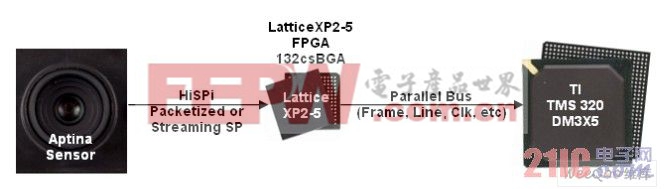

一個實際例子是,針對Aptina Imaging的HiSPi串行接口至TI DSP并行接口的橋接,LatticeXP2-5非易失性FPGA提供了高效、具有成本效益的解決方案,如圖4所示。

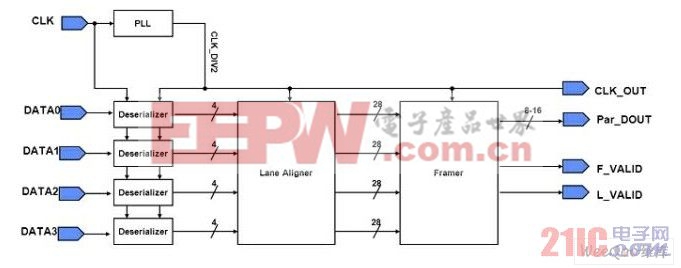

該參考設計在輸入端用HiSPi串行接口,在輸出端用TI TMS320DM3X5連接至Aptina傳感器。*估硬件已測試了Aptina的A-1000傳感器MT9M034/MTM024和MT9J003。該參考設計支持分組(Packetized)和Streaming SP HiSPi格式:1-4通道運行速度高達每通道700Mbps。它還模擬并行傳感器輸出,輸出總線寬度為8、10、12、14或16位。并行接口可配置為1.8V、2.5V或3.3V LVCMOS電平。參考設計的模塊圖如圖5所示。

圖5 參考設計的模塊圖

FPGA在傳感器接口橋接上的挑戰

可編程邏輯作為圖像傳感器和ASSP之間的橋接面臨三個方面的挑戰。首先,FPGA必須為接口信號提供電信號支持。第二,FPGA的I/O必須有足夠的gearing邏輯來支持快速串行傳感器接口。第三,FPGA必須提供符合成本效益的非常小的外形尺寸,以適應現代攝像機對于緊湊外形的要求。

具有完備子LVDS文檔支持的LatticeXP2非易失FPGA系列已被證實解決了圖像傳感器橋接的電氣需求。集成PLL、專用時鐘沿和I/O gearing邏輯解決了高速串行傳感器接口。最后,萊迪思半導體(Lattice)的 XP2提供了具有成本效益的8×8mm面積。此外,由于其非易失的特性,LatticeXP2系列器件無需外部引導PROM,從而進一步節省了電路板空間,這使得他們成為傳感器接口的具有吸引力的可編程邏輯平臺。圖像信號處理(ISP)IP的可用性也使更大型的LatticeXP2器件可提供各種功能,如傳感器數據線性化、傳感器寄存器編程、去Bayering、有缺陷的像素校正、伽瑪校正和每個色通道高達24位的簡單HDR。

評論