基于FPGA的攝像機傳感器接口實現

如今有幾個著名的圖像傳感器制造商,它們是Aptina、OmniVision Technologies、索尼、三星、松下、東芝和Altasens。

如前所述,傳感器制造商配置了一系列接口,用于將離開其芯片的圖像信號傳至下游邏輯進行處理。非常普遍的是,同一傳感器制造商根據需要從芯片中提取的數據量使用不同的接口。例如,具有兆像素分辨率的現代傳感器需要在給定的周期時間傳出比僅具有VGA級分辨率的傳感器多得多的數據。像高動態范圍(HDR)這樣的要求還增加了數據量,需要從每個圖像幀的圖像傳感器讀取數據,而為支持平滑、低延遲高品質的視頻,需要在給定的時間內從傳感器芯片提取幀數,這也影響了傳感器接口的選擇。

圖像傳感器接口的演進

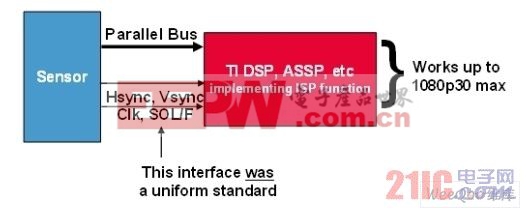

到目前為止,所有傳感器都可連接到并行LVCMOS接口,如圖2所示。傳感器分辨率和幀速率已經提高到一個水平,此時以前的主流CMOS并行接口已不能處理所要求的帶寬。

圖2 并行LVCMOS圖像傳感器I/F

由于兆像素傳感器的問世,對更高速度的需求激增,HDR和對支持更高幀速率、新型、更高速度傳感器的需求正使用不同的接口來克服并行LVCMOS的局限性。例如,索尼和松下使用并行的子LVDS接口,OmniVision使用MIPI或串行LVDS。另一個例子是,為支持更高帶寬的需求,Aptina Imaging已經推出了稱為HiSPi(高速串行像素接口)的高速串行接口。HiSPi接口可以工作在1-4個串行數據通道,加上1個時鐘通道。每個信號是子LVDS差分信號,以 0.9V的共模電壓為中心。每個通道可以運行在高達700Mbps下。

HiSPi與并行傳感器接口橋接的需求

多個傳感器接口給標準化下游視頻處理邏輯的制造商提出了一個問題,因為用一個ASSP支持許多不同的傳感器接口非常困難。

大多數ISP(圖像信號處理)器件支持傳統的CMOS并行傳感器接口,但通常缺乏對高速串行接口的支持。很多ISP并行接口的運行速度遠遠超過了傳感器的并行接口。但是,由于傳感器已遷移到不同串行接口,ISP器件需要邏輯以轉換到并行接口。因此FPGA橋接器件需要將高速串行數據轉換到并行格式。對于視頻信號處理ASSP的制造商(他們擁有支持更快的并行CMOS傳感器接口的現成產品),FPGA解決了連接至高速串行傳感器的問題。FPGA提供在高速傳感器和傳統圖像信號處理ASSP之間的簡單、具有成本效益的可編程橋接。這個概念如圖3所示。

圖3 高速圖像傳感器和ASSP之間的可編程橋接

評論