超低抖動(dòng)時(shí)鐘合成器的設(shè)計(jì)挑戰(zhàn)

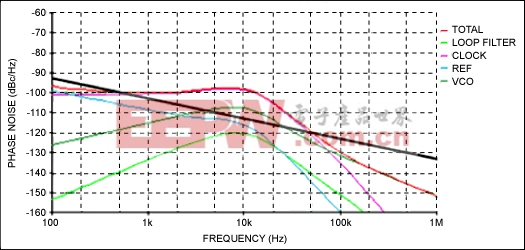

除了PFD噪聲,濾波器設(shè)置接近于10kHz時(shí)的VCO噪聲峰值。剩下的主要問(wèn)題是參考時(shí)鐘噪聲,不幸的是,40kHz以上優(yōu)于模板性能不足以消除該噪聲。所以,需要采用其它類型的振蕩器來(lái)滿足相噪要求,例如:OCXO。

該設(shè)計(jì)的印刷電路板(PCB)可以適用三種或四種不同的XO引腳排列。圖7給出了采用Vectron OCXO的仿真結(jié)果。即使考慮鑒相器噪聲,最終的抖動(dòng)為86.5fs。該抖動(dòng)留出一定裕量給沒(méi)有考慮的分頻器噪聲(該噪聲應(yīng)該沒(méi)有明顯的負(fù)面影響)和可能需要的放大器。

圖7. 使用Vectron OXCO的仿真結(jié)果:4GHz下的相噪

本文引用地址:http://www.104case.com/article/161856.htm

結(jié)論

2GHz時(shí)達(dá)到100fs的抖動(dòng)指標(biāo)要比我們預(yù)計(jì)的更難實(shí)現(xiàn)。實(shí)驗(yàn)數(shù)據(jù)表明,利用一些標(biāo)準(zhǔn)的PLL電路可以達(dá)到這一目標(biāo)。關(guān)鍵在于VCO和參考時(shí)鐘的選擇。實(shí)驗(yàn)證明,UMX的VCO具有一流的相噪性能。剩下的兩個(gè)難題是:(1)選擇噪聲足夠低的參考時(shí)鐘;(2)選擇合適的放大器。幸運(yùn)的是,我們有很多器件可供選擇,同樣的電路布局可以適用于不同型號(hào)的引腳排列。放大器的選擇比較困難,需要進(jìn)一步分析以確定是否可以將其置于環(huán)路,還需考慮其噪聲的影響。

¹考慮到兩個(gè)單邊帶,文中在根號(hào)的內(nèi)外均包含了系數(shù)2。總的噪聲功率為SSB噪聲功率的2倍,因此總的噪聲電壓應(yīng)當(dāng)?shù)扔赟SB噪聲電壓。

²指的是單個(gè)元件,而不是模塊。

³在1MHz附近具有很高的相位噪聲,但是環(huán)路濾波器有助于衰減該噪聲。

評(píng)論