基于VHDL的MTM總線主模塊有限狀態(tài)機設計

1.2 MTM主模塊

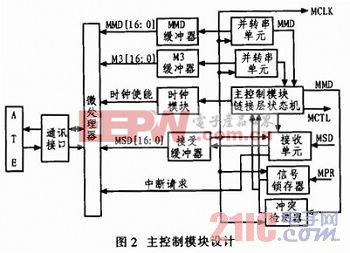

主控制模塊設計如圖2所示。主控制模塊在MTM總線協議中處于主控地位,主要功能是將來自微處理器的數據按照IEEE1149.5標準定義的消息格式進行打包送到指定的從控制模塊;同時將來自指定從控制模塊的消息包進行解包,并且提取有用數據傳回微處理器,供微處理器分析和處理。本文引用地址:http://www.104case.com/article/160361.htm

主狀態(tài)機是主控制模塊的核心單元,它的作用是控制整個信息傳輸過程。

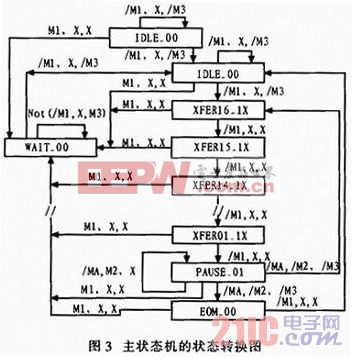

主狀態(tài)機的狀態(tài)轉換圖如圖3。當主狀態(tài)機處于某個給定的狀態(tài)時,MCTL和MMD信號的邏輯值在MCLK的上升沿產生;在每個MCLK信號周期,主狀態(tài)機根據控制信號的只發(fā)生狀態(tài)轉換;在主狀態(tài)機的17個傳送狀態(tài)下發(fā)送17位的數據包,其他狀態(tài)不發(fā)送數據,同時接收MSD上的數據;在每個數據包發(fā)送后,主狀態(tài)機至少保持在暫停狀態(tài)不少于4個MCLK周期,若當前接收的MSD數據有效則使接收單元使能信號有效;當主狀態(tài)機進入結束狀態(tài)時,當前消息傳送結束。

2 基于VHDL的主模塊有限狀態(tài)機的的設計

VHDL主要用于描述數字系統(tǒng)的結構、行為、功能和接口,同時支持層次化和模塊化設計,并且可以進行仿真和綜合。

數字電路分為組合邏輯電路和時序邏輯電路兩種。組合邏輯電路的輸出只與當前輸入有關,時序邏輯電路的輸出與當前輸入和過去輸入都有關。狀態(tài)機是一種廣義的時序電路,一般包括用于狀態(tài)譯碼和產生輸出信號組合邏輯和存儲狀態(tài)的寄存器邏輯兩部分。

根據MTM總線主模塊的狀態(tài)轉換圖,其基于VHDL有限狀態(tài)機的代碼如下:

評論